Maksymalizacja gęstości mocy i parametrów działania w przetwornicach przełączających z użyciem podwójnych tranzystorów MOSFET

2024-02-27

Przemysłowe i motoryzacyjne przetwornice przełączające oraz sterowniki silników wymagają polowych tranzystorów z tlenku metalu (MOSFET) o niewielkich wymiarach, które są wydajne i generują minimalne zakłócenia elektryczne. Wymagania te pomaga spełnić podejście z zastosowaniem podwójnych tranzystorów MOSFET.

Dobrze zaprojektowane podwójne tranzystory MOSFET w jednej obudowie zajmują mniej miejsca na płytce drukowanej (PCB), zmniejszają indukcyjność pasożytniczą i eliminują potrzebę stosowania dużych i kosztownych radiatorów poprzez poprawę parametrów termicznych. Takie urządzenia mogą wykonywać operacje przełączania bez zakłóceń przy częstotliwości kilkuset kiloherców (kHz), działać stabilnie w szerokim zakresie temperatur i charakteryzują się niskim prądem upływu. Jednak, aby w pełni wykorzystać zalety tych części, projektanci muszą zrozumieć ich charakterystykę roboczą.

W niniejszym artykule przedstawiono przykłady podwójnych tranzystorów MOSFET firmy Nexperia i pokazano, w jaki sposób projektanci mogą z nich korzystać, aby realizować wytrzymałe i wysokosprawne projekty o ograniczonych rozmiarach. Omówiono w nim sposoby optymalizacji projektów obwodów i płytek drukowanych oraz zawarto wskazówki dotyczące symulacji elektrotermicznej i analizy strat.

Wyższa sprawność przy dużej szybkości przełączania

Podwójne tranzystory MOSFET są odpowiednie do wielu zastosowań motoryzacyjnych (AEC-Q101) i przemysłowych, na przykład do przetwornic przełączających prądu stałego, przemienników silników i kontrolerów zaworów elektromagnetycznych. W zastosowaniach tych można wykorzystywać podwójne tranzystory MOSFET w topologiach z parami przełączników i topologiach półmostkowych.

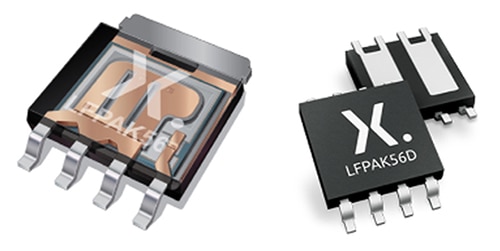

Seria LFPAK56D firmy Nexperia jest godnym uwagi przykładem podwójnych tranzystorów MOSFET. Wykorzystują one technologię zacisków miedzianych firmy Nexperia, która zapewnia wyjątkową obciążalność prądową, niską impedancję obudowy i wysoką niezawodność (ilustracja 1, po prawej). Te zaciski z litej miedzi poprawiają rozpraszanie ciepła z podłoża półprzewodnikowego przez połączenia lutowane do płytki drukowanej, umożliwiając przepływ około 30% całkowitego odprowadzanego ciepła przez wtyki źródła. Duże przekroje miedzi obniżają również straty mocy rezystancyjnej i tłumienie oscylacji komutacyjnych poprzez zmniejszenie indukcyjności pasożytniczej linii.

Ilustracja 1: w obudowie LFPAK56D (po prawej) umieszczono dwa niezależne tranzystory MOSFET i wykorzystano struktury zacisków miedzianych podobne do obudowy LFPAK56 zawierającej jeden tranzystor MOSFET (po lewej). (Źródło ilustracji: Nexperia)

Ilustracja 1: w obudowie LFPAK56D (po prawej) umieszczono dwa niezależne tranzystory MOSFET i wykorzystano struktury zacisków miedzianych podobne do obudowy LFPAK56 zawierającej jeden tranzystor MOSFET (po lewej). (Źródło ilustracji: Nexperia)

Podobnie jak większość części przeznaczonych do wysokonapięciowych przetwornic przełączających, urządzenie LFPAK56D wykorzystuje technologię superzłączową. Taka konstrukcja zmniejsza rezystancję dren-źródło w stanie włączenia (RDS(on)) oraz ładunek bramka-dren (QGD), minimalizując straty mocy. Działanie dwóch tranzystorów MOSFET na tym samym podłożu dodatkowo zmniejsza rezystancję dren-źródło.

Seria LFPAK56D to superzłączowe tranzystory MOSFET, które są odporne na zjawiska lawinowe i charakteryzują się szerokim bezpiecznym obszarem roboczym (SOA). Na przykład każdy ze 100-woltowych tranzystorów MOSFET w urządzeniu TrenchMOS PSMN029-100HLX posiada rezystancję RDS(on) wynoszącą 29mΩ, może obsłużyć moc 68W i przewodzić prąd do 30A.

W serii LFPAK56D zastosowano również technologię SchottkyPlus firmy NXP, która zmniejsza impulsy i prądy upływu. Na przykład typowa rezystancja RDS(on) dla urządzenia PSMN014-40HLDX wynosi 11,4mΩ, a prąd upływu dren-źródło jest bardzo niski - 10nA.

Aby w pełni wykorzystać wysokie prądy tranzystorów MOSFET, płytka drukowana musi być zaprojektowana tak, aby rozpraszać duże ilości ciepła i zapewniać stabilne połączenia elektryczne. Wielowarstwowe płytki drukowane z wystarczającą liczbą przelotek i dużych, grubych ścieżek miedzianych zapewniają wysokie parametry termiczne.

Zapobieganie niekontrolowanemu wzrostowi temperatury

Podczas gdy tranzystory mocy MOSFET po pełnym włączeniu są stabilne termicznie, niekontrolowany wzrost temperatury stwarza ryzyko, gdy prąd drenu (ID) jest niski.W tym stanie roboczym miejscowe nagrzewanie ma tendencję do obniżania progowego napięcia bramka-źródło (VGS(th)), co oznacza, że urządzenie włącza się łatwiej. Stwarza to dodatnie sprzężenie zwrotne, któremu towarzyszy dodatkowy prąd powodujący większe nagrzewanie i jeszcze niższą wartość napięcia VGS(th).

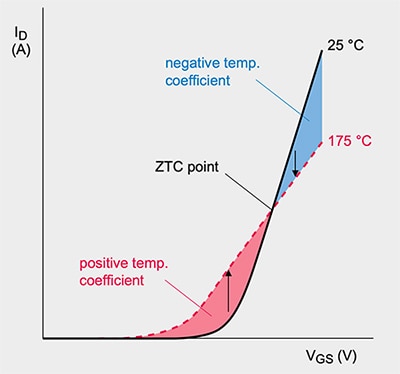

Ilustracja 2 przedstawia ten efekt dla stałego napięcia dren-źródło (VDS). Wraz ze wzrostem napięcia VGS występuje krytyczne natężenie prądu ID znane jako zerowy współczynnik temperaturowy (ZTC). Powyżej tej wartości prądu występuje ujemne sprzężenie zwrotne i stabilność termiczna (strefa niebieska), natomiast poniżej dominuje spadek napięcia progowego, co skutkuje niestabilnością termiczną punktów pracy, które mogą prowadzić do niekontrolowanego wzrostu temperatury (czerwona strefa).

Ilustracja 2: poniżej punktu ZTC tranzystor MOSFET może wejść w niekontrolowany wzrost temperatury ze względu na termicznie wywoływany spadek napięcia VGS (czerwony obszar). (Źródło ilustracji: Nexperia)

Ilustracja 2: poniżej punktu ZTC tranzystor MOSFET może wejść w niekontrolowany wzrost temperatury ze względu na termicznie wywoływany spadek napięcia VGS (czerwony obszar). (Źródło ilustracji: Nexperia)

Efekt ten zmniejsza bezpieczny obszar roboczy (SOA) przy niskich prądach i wysokich napięciach dren-źródło. Nie stanowi to istotnego problemu w przypadku szybkich operacji przełączania ze stromym nachyleniem dV/dt. Jednak wraz z wydłużeniem czasu przełączania, np. w celu zmniejszenia zakłóceń elektromagnetycznych, istnieje większe prawdopodobieństwo niestabilności termicznej, a tym samym jest ona potencjalnie bardziej niebezpieczna.

Niższe straty przełączania przy wysokich częstotliwościach

Przy doborze superzłączowego tranzystora MOSFET do zastosowań szybkiego przełączania, zasadnicze znaczenie ma niski ładunek QGD, ponieważ znacznie zmniejsza straty przełączania.

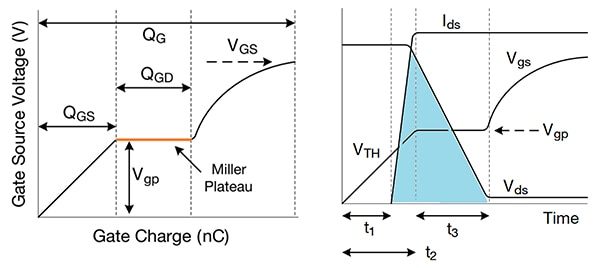

Duże straty mocy występują podczas przełączania, gdy między drenem, bramką i źródłem jednocześnie występują znaczne zmiany napięcia i prądu. Niski ładunek QGD skutkuje krótkim plateau Millera (ilustracja 3, po lewej), prowadzącym do stromego zbocza przełączania (dVds/dt), co ostatecznie skutkuje mniejszymi dynamicznymi stratami energii podczas włączania (ilustracja 3, niebieski obszar po prawej stronie).

Ilustracja 3: krótkie plateau Millera (po lewej) oznacza strome zbocze przełączania, skutkujące niskimi stratami dynamicznymi (niebieski obszar po prawej). Vgp to napięcie bramka-źródło plateau Millera. VTH jest napięciem progowym bramki. IDS to prąd dren-źródło. (Źródło ilustracji: Vishay)

Ilustracja 3: krótkie plateau Millera (po lewej) oznacza strome zbocze przełączania, skutkujące niskimi stratami dynamicznymi (niebieski obszar po prawej). Vgp to napięcie bramka-źródło plateau Millera. VTH jest napięciem progowym bramki. IDS to prąd dren-źródło. (Źródło ilustracji: Vishay)

Ograniczanie energii lawinowej i ochrona tranzystorów MOSFET

W momencie wyłączenia cewki stojana w układzie napędowym silnika, zanikające pole magnetyczne utrzymuje przepływ prądu, generując wysokie napięcie indukcyjne na tranzystorze MOSFET, które nakłada się na napięcie zasilania (VDD). Jednak napięcie przebicia w stanie zaporowym (VBR) diody podłożowej tranzystora MOSFET ogranicza to wysokie napięcie. W tzw. zjawisku lawinowym tranzystory MOSFET zamieniają wychodzącą energię magnetyczną na energię lawinową (EDS), aż prąd cewki spadnie do zera. Może to szybko spowodować przegrzanie kryształu półprzewodnika.

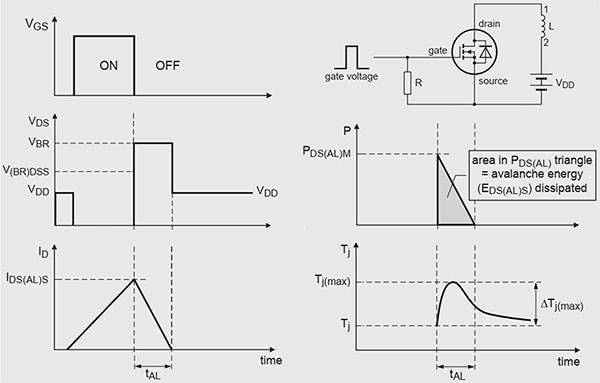

Ilustracja 4 przedstawia proste sterowanie cewką za pomocą przełącznika MOSFET oraz sygnały czasowe przed jednym zdarzeniem lawinowym, w jego trakcie (okno czasowe tAL) oraz po nim. Zbyt duża ilość rozpraszanej energii lawinowej (EDS(AL)S) powoduje uszkodzenie struktury półprzewodnika przez powstałe ciepło.

Ilustracja 4: sygnały czasowe tranzystora MOSFET przed pojedynczym zdarzeniem lawinowym, w jego trakcie (tAL) oraz po nim. (Źródło ilustracji: Nexperia)

Ilustracja 4: sygnały czasowe tranzystora MOSFET przed pojedynczym zdarzeniem lawinowym, w jego trakcie (tAL) oraz po nim. (Źródło ilustracji: Nexperia)

Próby laboratoryjne przeprowadzone przez firmę Nexperia wykazały, że tranzystory MOSFET LFPAK56D są bardzo wytrzymałe i mogą wytrzymać kilka miliardów zdarzeń lawinowych bez uszkodzeń. Biorąc pod uwagę maksymalną energię lawinową, w stopniach sterowników cewek można zrezygnować z dodatkowych diod ograniczających czy poziomujących i wykorzystywać tylko działanie lawinowe tych tranzystorów MOSFET.

Elektrotermiczna symulacja online

Opieranie się na prostym współczynniku dobroci (FOM), takim jak iloczyn RDS x QGD, jest niewystarczające dla poprawy sprawności układu. Zamiast tego projektanci muszą przeprowadzić bardziej precyzyjną analizę strat, która uwzględnia straty tranzystora MOSFET spowodowane przez:

- Przewodność w stanie włączenia

- Straty włączania i wyłączania

- Ładowanie i rozładowywanie pojemności wyjściowej

- Straty przewodzenia ciągłego i przełączania diody podłożowej

- Ładowanie i rozładowywanie pojemności bramki

Aby zminimalizować straty całkowite, projektanci muszą zrozumieć zależność między parametrami tranzystora MOSFET a środowiskiem pracy. W tym celu firma Nexperia oferuje precyzyjne modele elektrotermiczne tranzystorów MOSFET, które łączą w sobie parametry elektryczne i termiczne oraz reprezentują wszystkie ważne zachowania tranzystorów MOSFET. Deweloperzy mogą skorzystać z symulatora online PartQuest Explorer lub importować modele w formacie SPICE i VHDL-AMS na wybraną platformę symulacyjną.

W momencie pisania tego tekstu dostępne są modele elektryczne tylko dla tranzystorów MOSFET LFPAK56D. Dlatego poniższy przykład symulacji termicznej dotyczy tranzystora MOSFET innego typu, BUK7S1R0-40H.

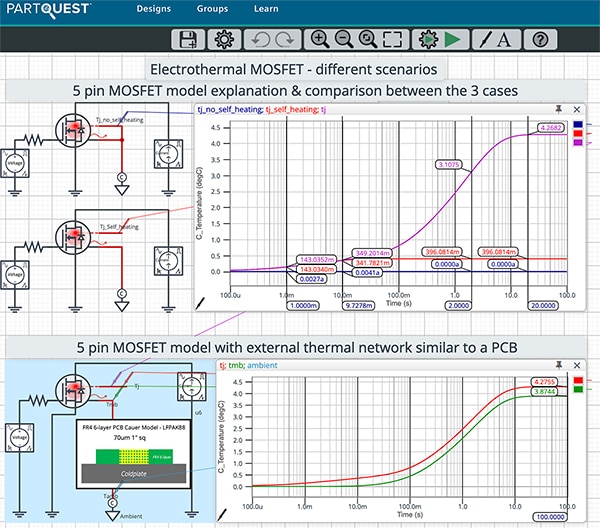

W ramach interaktywnego eksperymentu pt. Modele elektrotermiczne IAN50012 dla tranzystorów mocy MOSFET, przeprowadzono symulację trzech scenariuszy nagrzewania tranzystora BUK7S1R0-40H po włączeniu prądu obciążenia 36,25A. Ilustracja 5 przedstawia trzy konfiguracje symulacji po lewej stronie.

Ilustracja 5: symulacja elektrotermiczna tranzystora MOSFET z wykorzystaniem symulatora online PartQuest Explore. (Źródło ilustracji: Nexperia)

Ilustracja 5: symulacja elektrotermiczna tranzystora MOSFET z wykorzystaniem symulatora online PartQuest Explore. (Źródło ilustracji: Nexperia)

W górnym scenariuszu „tj_no_self_heating” złącze i podstawa montażowa są bezpośrednio sprzężone z temperaturą otoczenia (Tamb) 0°C, bez oporu cieplnego (Rth). W środkowym scenariuszu „tj_self_heating,” układ półprzewodnikowy jest sprzężony przez Rth-j, a Tj wzrasta o około 0,4°C. Dolny scenariusz przedstawia podstawę montażową (mb) sprzężoną z temperaturą otoczenia za pośrednictwem Rth_mb sześciowarstwowej płytki FR4 z radiatorem. Tmb (kolor zielony) wzrasta do 3,9°C, a Tj (kolor czerwony) wzrasta do 4,3°C.

Podsumowanie

\Tranzystory MOSFET LFPAK56D o ultraniskich stratach zapewniają znakomitą sprawność i gęstość mocy w szybko przełączających przetwornicach lub sterownikach silników. Zagadnienia dotyczące projektowania obwodów i termicznych płytek drukowanych oraz omówione tutaj symulacje elektrotermiczne ilustrują, w jaki sposób projektanci mogą osiągnąć wytrzymałość oraz wysoką sprawność w ograniczonej przestrzeni.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.