Zastosowanie szybkiej metody FPGA do tworzenia zastosowań sztucznej inteligencji brzegowej o wysokiej efektywności i sprawności energetycznej

Przekazane przez: Północnoamerykańscy redaktorzy DigiKey

2021-01-12

Projektanci, którzy chcą wdrażać algorytmy sztucznej inteligencji (AI) na procesorach wnioskowania na obrzeżach systemów, znajdują się pod stałą presją, aby zmniejszać zużycie energii i skracać czas opracowywania przy jednoczesnym wzroście wymagań dotyczących przetwarzania. Bezpośrednio programowalne macierze bramek (FPGA) oferują szczególnie skuteczne połączenie prędkości i sprawności energetycznej dla wdrożenia aparatów wnioskowania sieci neuronowych (NN) wymaganych dla sztucznej inteligencji brzegowej. Jednak deweloperom, którzy nie znają macierzy FPGA, konwencjonalne metody opracowywania rozwiązań FPGA mogą wydawać się skomplikowane, przez co często sięgają po nie w pełni optymalne rozwiązania.

W tym artykule opisano prostsze podejście oferowane przez firmę Microchip Technology, które pozwala deweloperom omijać tradycyjne opracowywanie rozwiązań FPGA, aby tworzyć szkolone sieci neuronowe (NN) z wykorzystaniem FPGA i zestawu rozwojowego oprogramowania (SDK), lub korzystać z bazującego na FPGA zestawu wideo, aby przejść bezpośrednio do tworzenia inteligentnych, wbudowanych zastosowań wizyjnych.

Dlaczego warto korzystać ze sztucznej inteligencji brzegowej?

Przetwarzanie brzegowe przynosi szereg korzyści dla zastosowań Internetu rzeczy (IoT) w tak różnych segmentach, jak automatyka przemysłowa, systemy bezpieczeństwa, inteligentne domy itp. W zastosowaniu przemysłowego Internetu rzeczy (IIoT) przeznaczonym dla zakładów produkcyjnych, przetwarzanie brzegowe może radykalnie poprawiać czas reakcji w pętlach sterowania procesami przez wyeliminowanie opóźnień powodowanych przez wymianę danych z aplikacjami opartymi na chmurze. Podobnie brzegowe systemy zabezpieczeń i inteligentne zamki drzwi wejściowych mogą nadal funkcjonować nawet w razie przypadkowego lub celowego przerwania połączenia z chmurą. W wielu przypadkach użycie przetwarzania brzegowego w tych zastosowaniach może obniżyć ogólne koszty operacyjne przez ograniczenie zależności produktu od zasobów chmurowych. Zamiast mieć do czynienia z nieoczekiwanym zapotrzebowaniem na dodatkowe, drogie zasoby chmurowe w miarę wzrostu popytu na swoje produkty, deweloperzy mogą polegać na lokalnych mocach obliczeniowych wbudowanych w te produkty, aby zapewnić stabilność kosztów operacyjnych.

Szybka akceptacja i zwiększone zapotrzebowanie na modele wnioskowania oparte na uczeniu maszynowym (ML) radykalnie wzmacniają znaczenie przetwarzania brzegowego. Lokalne przetwarzanie modeli wnioskowania pomaga deweloperom zredukować opóźnienia reakcji i koszty zasobów chmurowych wymaganych do wnioskowania w oparciu o chmurę. Użytkownikom zaś korzystanie z lokalnych modeli wnioskowania dodaje pewności, że ich produkty będą nadal funkcjonować pomimo sporadycznej utraty łączności z Internetem lub zmian w ofercie dostawcy produktów w chmurze. Ponadto obawy o bezpieczeństwo i prywatność mogą jeszcze bardziej zwiększyć zapotrzebowanie na przetwarzanie lokalne i spowodować ograniczenie ilości wrażliwych informacji przekazywanych do chmury za pośrednictwem publicznego Internetu.

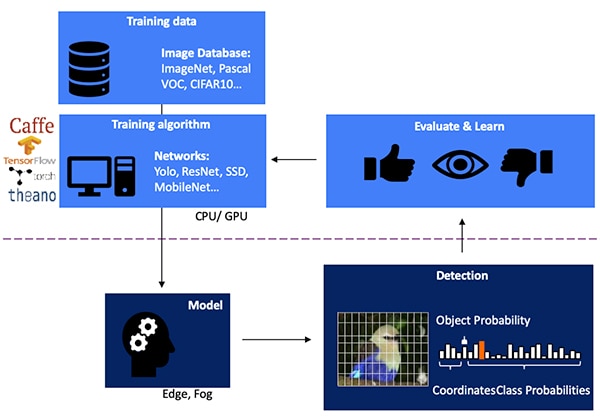

Opracowanie modelu wnioskowania w sieci neuronowej (NN) do wizyjnego wykrywania przedmiotów jest procesem wieloetapowym, rozpoczynającym się od szkolenia modelu, zwykle wykonywanego w środowisku uczenia maszynowego (ML), takim jak biblioteka TensorFlow, z wykorzystaniem publicznie dostępnych lub własnych obrazów oznakowanych. Ze względu na wymagania związane z przetwarzaniem danych, szkolenie modelu jest zazwyczaj przeprowadzane z wykorzystaniem procesorów graficznych (GPU) w chmurze lub na innej platformie obliczeniowej o wysokiej wydajności. Po zakończeniu szkolenia model jest przekształcany w model wnioskowania zdolny do pracy na rozproszonych zasobach obliczeniowych (tzw. mgle obliczeniowej) i dostarczania wyników wnioskowania jako zbioru prawdopodobieństw klas obiektów (ilustracja 1).

Ilustracja 1: wdrożenie modelu wnioskowania dla sztucznej inteligencji brzegowej stanowi zakończenie wieloetapowego procesu wymagającego szkolenia i optymalizacji sieci neuronowych w środowiskach korzystających z dostępnych lub niestandardowych danych szkoleniowych. (Źródło ilustracji: Microchip Technology)

Ilustracja 1: wdrożenie modelu wnioskowania dla sztucznej inteligencji brzegowej stanowi zakończenie wieloetapowego procesu wymagającego szkolenia i optymalizacji sieci neuronowych w środowiskach korzystających z dostępnych lub niestandardowych danych szkoleniowych. (Źródło ilustracji: Microchip Technology)

Dlaczego modele wnioskowania stanowią wyzwanie obliczeniowe

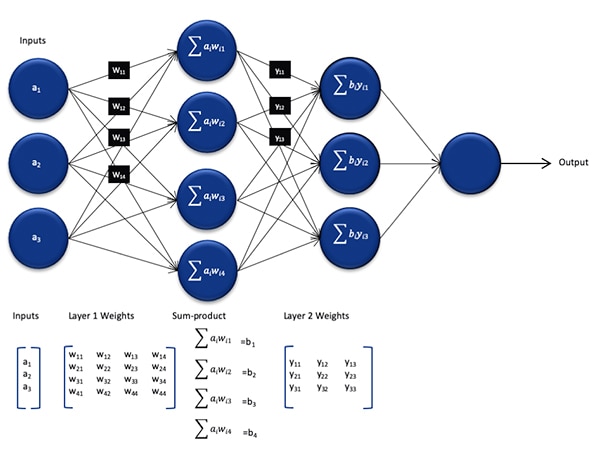

Chociaż model wnioskowania w sieci neuronowej jest mniejszy i mniej skomplikowany w porównaniu z modelem stosowanym podczas procesu szkolenia, nadal stanowi wyzwanie obliczeniowe dla procesorów ogólnego przeznaczenia ze względu na dużą liczbę wymaganych obliczeń. W swojej ogólnej postaci model głęboki sieci neuronowej składa się z wielu warstw zbiorów neuronów. W każdej warstwie w pełni połączonej sieci każdy neuron nij musi obliczać sumę iloczynów każdego wejścia z uwzględnieniem odpowiedniej wagi wij (ilustracja 2).

Ilustracja 2: liczba obliczeń wymaganych do wnioskowania za pomocą sieci neuronowej może stanowić poważne obciążenie obliczeniowe. (Źródło ilustracji: Microchip Technology)

Ilustracja 2: liczba obliczeń wymaganych do wnioskowania za pomocą sieci neuronowej może stanowić poważne obciążenie obliczeniowe. (Źródło ilustracji: Microchip Technology)

Ilustracja 2 nie przedstawia dodatkowych wymagań obliczeniowych nałożonych przez funkcję aktywacji, która modyfikuje wyjście każdego neuronu przez mapowanie wartości ujemnych na zero, mapowanie wartości większych niż 1 na 1 i podobne funkcje. Wyjście funkcji aktywacji każdego neuronu nij służy jako wejście dla następnej warstwy i+1, i tak dalej w każdej warstwie. Na końcu warstwa wyjściowa modelu NN generuje wektor wyjściowy reprezentujący prawdopodobieństwo, że pierwotny wektor wejściowy (lub macierz) odpowiada jednej z klas (lub etykiet) używanych podczas nadzorowanego procesu uczenia się.

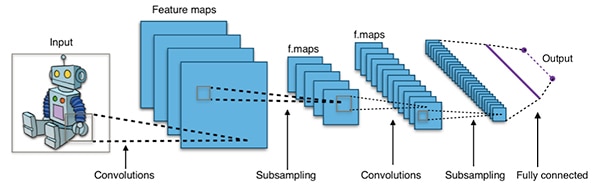

Skuteczne modele sieci neuronowych tworzone są z wykorzystaniem architektur, które są znacznie większe i bardziej złożone, niż typowa, ogólna architektura sieci neuronowej przedstawiona powyżej. Na przykład typowa konwolucyjna sieć neuronowa (CNN) używana do wykrywania przedmiotów w obrazie stosuje te zasady w sposób fragmentaryczny, skanując szerokość, wysokość i głębię kolorów obrazu wejściowego w celu utworzenia serii map cech, które ostatecznie dają wyjściowy wektor przewidywania (ilustracja 3).

Ilustracja 3: sieci CNN używane do wykrywania przedmiotów w obrazie obejmują dużą liczbę neuronów w wielu warstwach, stanowiąc bardzo duże obciążenie dla platformy obliczeniowej. (Źródło ilustracji: Aphex34 CC BY-SA 4.0)

Ilustracja 3: sieci CNN używane do wykrywania przedmiotów w obrazie obejmują dużą liczbę neuronów w wielu warstwach, stanowiąc bardzo duże obciążenie dla platformy obliczeniowej. (Źródło ilustracji: Aphex34 CC BY-SA 4.0)

Wykorzystanie macierzy bramek FPGA do przyspieszenia obliczeń w sieci neuronowej

Mimo że nadal pojawia się szereg opcji wykonywania modeli wnioskowania na brzegu systemu, niewiele alternatyw zapewnia optymalne połączenie elastyczności, wydajności i sprawności energetycznej, które są niezbędne do wykonywania w praktyce szybkiego wnioskowania na jego brzegu. Wśród łatwo dostępnych alternatyw dla sztucznej inteligencji brzegowej, układy FPGA są szczególnie efektywne, ponieważ mogą zapewnić wysokowydajne, sprzętowe wykonywanie wymagających obliczeniowo operacji przy stosunkowo niewielkim zużyciu energii.

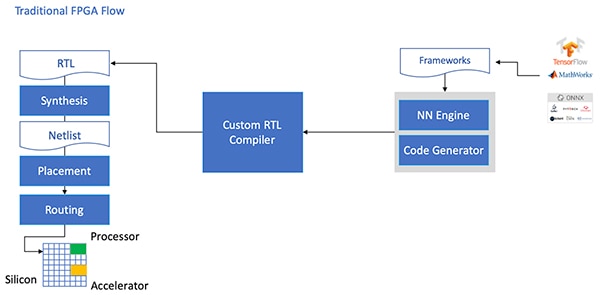

Pomimo zalet, układy FPGA są czasami pomijane z powodu tradycyjnego toku prac rozwojowych, który może być zniechęcający dla deweloperów bez bogatego doświadczenia z macierzami bramek FPGA. Aby stworzyć skuteczne wdrożenie FPGA modelu sieci neuronowej NN wygenerowanego przez środowisko sieci neuronowej, deweloper musiałby rozumieć niuanse przekształcania modelu na język RTL, syntezowania projektu oraz opracowania końcowego, fizycznego projektu miejsca i trasy w celu uzyskania optymalnego wdrożenia (ilustracja 4).

Ilustracja 4: aby wdrożyć model sieci neuronowej na układach FPGA, deweloperzy musieli dotychczas rozumieć sposób przekształcania modeli na język RTL i opracowywać tradycyjny przepływ FPGA. (Źródło ilustracji: Microchip Technology)

Ilustracja 4: aby wdrożyć model sieci neuronowej na układach FPGA, deweloperzy musieli dotychczas rozumieć sposób przekształcania modeli na język RTL i opracowywać tradycyjny przepływ FPGA. (Źródło ilustracji: Microchip Technology)

Dzięki macierzom bramek FPGA PolarFire, specjalnemu oprogramowaniu i związanej z nim własności intelektualnej (IP), firma Microchip Technology dostarcza rozwiązanie, które sprawia, że wysokowydajne wnioskowanie o niskim zużyciu energii na krawędzi systemu jest powszechnie dostępne dla deweloperów bez doświadczenia z macierzami bramek FPGA.

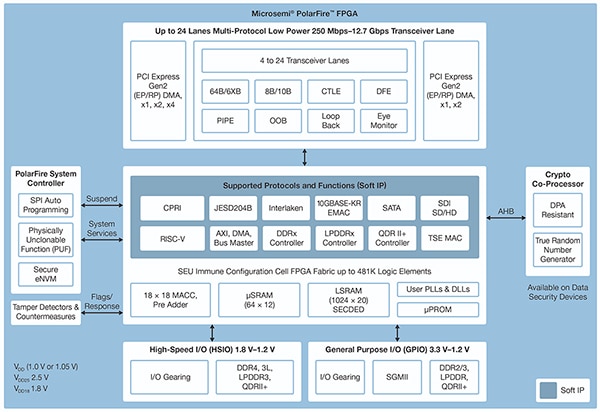

Wykonane w zaawansowanej, nieulotnej technologii procesowej, układy PolarFire FPGA zostały zaprojektowane w celu zmaksymalizowania elastyczności i wydajności przy jednoczesnym zminimalizowaniu zużycia energii. Wraz z szeroką gamą szybkich interfejsów do komunikacji i wejść-wyjść (I/O), wyposażone są w głęboką sieć szkieletową macierzy bramek FPGA zdolną do obsługi zaawansowanych funkcji przy użyciu rdzeni miękkich stanowiących własność intelektualną, w tym procesorów RISC-V, zaawansowanych kontrolerów pamięci i innych podsystemów interfejsów standardowych (ilustracja 5).

Ilustracja 5: architektura PolarFire firmy Microchip Technology zapewnia głęboką sieć szkieletową, zaprojektowaną, aby wspierać wymagania konstrukcji o wysokiej wydajności, w tym wdrożeń intensywnych obliczeniowo modeli wnioskujących. (Źródło ilustracji: Microchip Technology)

Ilustracja 5: architektura PolarFire firmy Microchip Technology zapewnia głęboką sieć szkieletową, zaprojektowaną, aby wspierać wymagania konstrukcji o wysokiej wydajności, w tym wdrożeń intensywnych obliczeniowo modeli wnioskujących. (Źródło ilustracji: Microchip Technology)

Sieć szkieletowa macierzy bramek FPGA PolarFire zapewnia obszerny zestaw elementów logicznych i wyspecjalizowanych bloków, obsługiwanych w różnych rolach przez różne elementy grupy macierzy bramek FPGA PolarFire, w tym serię MPF100T, MPF200T, MPF300T i MPF500T (tabela 1).

|

Tabela 1: w sieci szkieletowej PolarFire dostępne są różnorodne cechy i możliwości macierzy bramek FPGA. (Źródło tabeli: DigiKey, na podstawie arkusza danych PolarFire firmy Microchip Technology)

Wśród cech szczególnie interesujących dla przyspieszenia wnioskowania, architektura PolarFire zawiera dedykowany blok obliczeniowy, który zapewnia funkcję mnożenia i dodawania do akumulatora (MAC) o wielkości 18 bitów x 18 bitów ze znakiem i sumatorem wstępnym. Wbudowany tryb iloczynu skalarnego wykorzystuje pojedynczy blok obliczeniowy do wykonania dwóch 8-bitowych operacji mnożenia, zapewniając mechanizm zwiększenia wydajności przez wykorzystanie znikomego wpływu kwantyzacji modelu na dokładność.

Poza przyspieszeniem operacji matematycznych, architektura PolarFire pomaga złagodzić rodzaj przeciążenia pamięci spotykany przy implementacji modeli inferencyjnych na architekturach ogólnego przeznaczenia, wykorzystując małe pamięci rozproszone do przechowywania wyników pośrednich powstających podczas wykonywania algorytmu sieci neuronowej. Ponadto, wagi i wartości błędu systematycznego modelu NN mogą być przechowywane w pamięci tylko do odczytu (ROM) o współczynniku głębokości 16 na 18 bitów, zbudowanej z elementów logicznych umieszczonych w pobliżu bloku obliczeniowego.

W połączeniu z innymi cechami sieci szkieletowej macierzy bramek FPGA PolarFire bloki obliczeniowe stanowią fundament układu wyższego poziomu, czyli CoreVectorBlox IP, oferowanego przez firmę Microchip Technology. Architektura ta stanowi elastyczny aparat sieci neuronowej, zdolny do realizacji różnych jej typów. Oprócz zbioru rejestrów sterowania, procesor CoreVectorBlox IP zawiera trzy główne bloki funkcjonalne:

- Mikrokontroler: prosty procesor RISC-V z rdzeniem miękkim, który odczytuje duży obiekt binarny (BLOB) z oprogramowania układowego firmy Microchip i właściwy dla użytkownika plik BLOB sieci neuronowej z pamięci zewnętrznej. Steruje on ogólnymi operacjami procesora obrazu CoreVectorBlox, wykonując instrukcje z obiektu BLOB oprogramowania układowego.

- Procesor macierzy (MXP): Procesor z rdzeniem miękkim zawierający osiem 32-bitowych arytmetycznych jednostek logicznych (ALU) i zaprojektowany do wykonywania operacji na wektorach danych z wykorzystaniem operacji tensorowych na elementach, w tym dodawania, odejmowania, alternatywy rozłącznej, przesunięcia, mnożenia, iloczynu skalarnego i innych, z wykorzystaniem mieszanej precyzji 8, 16 i 32-bitowej, odpowiednio do potrzeb.

- Akcelerator sieci CNN: Przyspiesza operacje MXP z wykorzystaniem dwuwymiarowej tablicy funkcji MAC wdrożonych z wykorzystaniem bloków obliczeniowych, działając z precyzją 8-bitową.

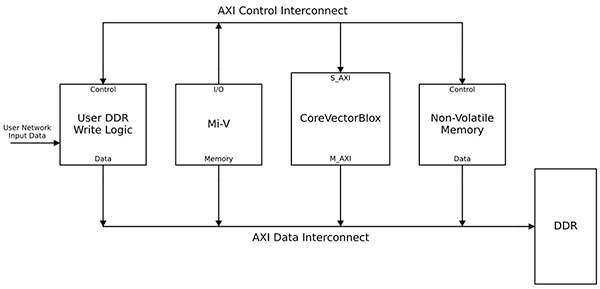

Kompletny system przetwarzania w sieci neuronowej zawiera blok CoreVectorBlox IP, pamięć, kontroler pamięci i procesor hosta, taki jak Microsoft Risc-V (Mi-V) z rdzeniem miękkim (ilustracja 6).

Ilustracja 6: blok CoreVectorBlox IP działa z procesorem hosta, takim jak mikrokontroler Mi-V RISC-V firmy Microchip, wdrażając model wnioskowania w sieci neuronowej. (Źródło ilustracji: Microchip Technology)

Ilustracja 6: blok CoreVectorBlox IP działa z procesorem hosta, takim jak mikrokontroler Mi-V RISC-V firmy Microchip, wdrażając model wnioskowania w sieci neuronowej. (Źródło ilustracji: Microchip Technology)

We wdrożeniu systemu wizyjnego procesor hosta ładuje oprogramowanie układowe i obiekty BLOB sieci z pamięci flash systemu i kopiuje je do pamięci RAM o podwójnej prędkości danych (DDR) do wykorzystania przez blok CoreVectorBlox. W miarę pojawiania się kadrów obrazu procesor hosta zapisuje je do pamięci DDR RAM i sygnalizuje blokowi CoreVectorBlox, aby rozpoczął przetwarzanie obrazu. Po uruchomieniu modelu wnioskowania zdefiniowanego w obiekcie BLOB sieci blok CoreVectorBlox zapisuje wyniki, w tym klasyfikację obrazu z powrotem do pamięci RAM DDR do wykorzystania przez aplikację docelową.

Tok prac rozwojowych upraszcza wdrożenie sieci neuronowej bazującej na macierzach bramek FPGA

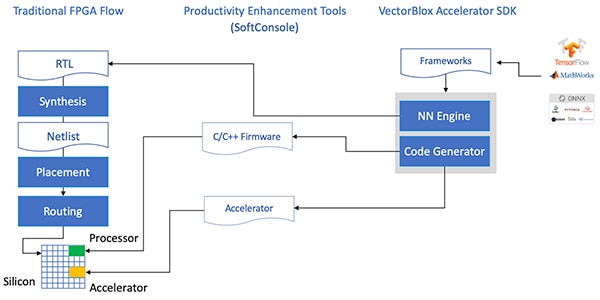

Firma Microchip chroni deweloperów przed złożonością wdrażania modelu wnioskowania w sieci neuronowej z wykorzystaniem macierzy bramek FPGA PolarFire. Zamiast zajmować się szczegółami tradycyjnego przepływu FPGA, deweloperzy modeli sieci neuronowych pracują tak jak zwykle ze swoimi środowiskami sieci neuronowych i ładują uzyskany model do zestawu rozwojowego oprogramowania (SDK) VectorBlox Accelerator. Zestaw SDK generuje wymagany zbiór plików, w tym pliki wymagane do zwykłego procesu opracowania macierzy bramek FPGA oraz wspomniane wcześniej oprogramowanie układowe i obiekt BLOB sieci (ilustracja 7).

Ilustracja 7: zestaw SDK oprogramowania VectorBlox Accelerator zarządza szczegółami wdrażania modelu sieci neuronowej w macierzy bramek FPGA, automatycznie generując pliki niezbędne do zaprojektowania i uruchomienia modelu wnioskowania bazującego na macierzach bramek FPGA. (Źródło ilustracji: Microchip Technology)

Ilustracja 7: zestaw SDK oprogramowania VectorBlox Accelerator zarządza szczegółami wdrażania modelu sieci neuronowej w macierzy bramek FPGA, automatycznie generując pliki niezbędne do zaprojektowania i uruchomienia modelu wnioskowania bazującego na macierzach bramek FPGA. (Źródło ilustracji: Microchip Technology)

Ponieważ zestaw SDK oprogramowania VectorBlox Accelerator nakłada projekt sieci neuronowej na aparat sieci neuronowej wdrażany w macierzach bramek FPGA, na tej samej konstrukcji macierzy bramek FPGA można uruchamiać różne sieci neuronowe bez potrzeby powtarzania syntezy konstrukcji macierzy bramek FPGA. Deweloperzy tworzą kod w języku C/C++ dla docelowego systemu i mogą przełączać „w locie” modele w systemie lub wykonywać modele równocześnie, korzystając z podziału czasu.

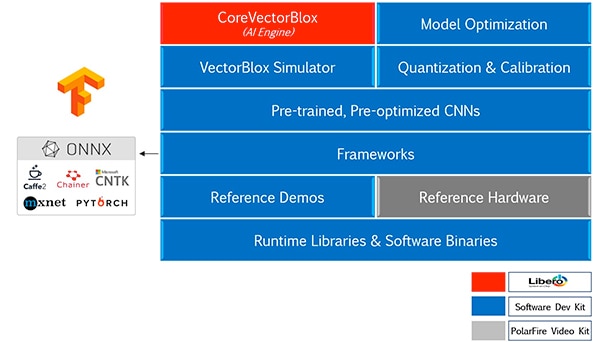

Zestaw SDK oprogramowania VectorBlox Accelerator łączy pakiet Libero do projektowania macierzy bramek FPGA firmy Microchip Technology z kompleksowym zestawem możliwości tworzenia modeli wnioskowania w sieciach neuronowych. Razem z usługami optymalizacji, kwantyzacji i kalibracji, zestaw SDK udostępnia symulator sieci neuronowych, który pozwala deweloperom korzystać z tych samych plików obiektu BLOB, aby sprawdzić model przed użyciem w sprzętowej implementacji macierzy bramek FPGA (ilustracja 8).

Ilustracja 8: zestaw SDK oprogramowania VectorBlox Accelerator zapewnia wszechstronny zestaw usług zaprojektowanych, aby zoptymalizować implementację modeli wnioskowania wygenerowanych przez to środowisko w macierzach bramek FPGA. (Źródło ilustracji: Microchip Technology)

Ilustracja 8: zestaw SDK oprogramowania VectorBlox Accelerator zapewnia wszechstronny zestaw usług zaprojektowanych, aby zoptymalizować implementację modeli wnioskowania wygenerowanych przez to środowisko w macierzach bramek FPGA. (Źródło ilustracji: Microchip Technology)

Zestaw SDK oprogramowania VectorBlox Accelerator obsługuje modele w formacie Open Neural Network Exchange (ONNX), a także modele generowane przez inne środowiska, takie jak TensorFlow, Caffe, Chainer, PyTorch i MXNET. Obsługiwane architektury sieci CNN obejmują MNIST, wersje MobileNet, ResNet-50, Tiny Yolo V2 i Tiny Yolo V3. Firma Microchip pracuje nad rozszerzeniem wsparcia w celu objęcia większości sieci dostępnych w wyszkolonych modelach z zestawu OpenVINO toolkit open model zoo, w tym Yolo V3, Yolo V4, RetinaNet i SSD-MobileNet, i wielu innych, dostępnych na zasadach open source.

Zestaw wizyjny demonstruje działanie wnioskowania w macierzy bramek FPGA

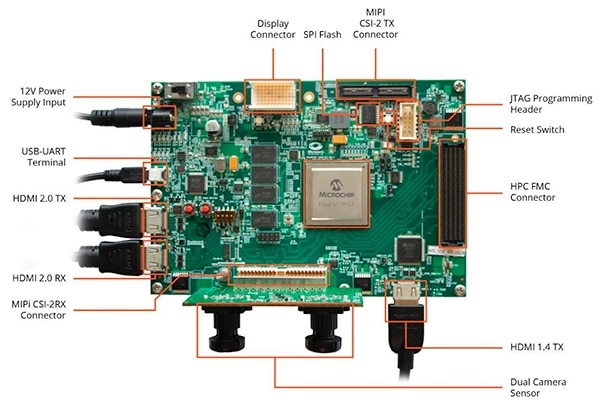

Aby pomóc deweloperom w szybkim przejściu do tworzenia inteligentnych zastosowań z wbudowanym przetwarzaniem danych wizyjnych, firma Microchip Technology udostępnia wszechstronną aplikację przykładową, która wykorzystuje zestaw MPF300-VIDEO-KIT do obsługi wideo i obrazów przez macierze bramek PolarFire FPGA i projekt referencyjny.

Wykorzystująca macierze bramek FPGA MPF300T PolarFire płytka zestawu łączy w sobie podwójny czujnik kamery, pamięć RAM DDR4, pamięć flash, zarządzanie energią i szereg interfejsów (ilustracja 9).

Ilustracja 9: zestaw MPF300-VIDEO-KIT do przetwarzania wideo i obrazów za pomocą macierzy bramek PolarFire FPGA i związane z nim oprogramowanie umożliwia deweloperom szybkie rozpoczęcie pracy z wnioskowaniem opartym na macierzach bramek FPGA w inteligentnych zastosowaniach z wbudowanym przetwarzaniem danych wizyjnych. (Źródło ilustracji: Microchip Technology)

Ilustracja 9: zestaw MPF300-VIDEO-KIT do przetwarzania wideo i obrazów za pomocą macierzy bramek PolarFire FPGA i związane z nim oprogramowanie umożliwia deweloperom szybkie rozpoczęcie pracy z wnioskowaniem opartym na macierzach bramek FPGA w inteligentnych zastosowaniach z wbudowanym przetwarzaniem danych wizyjnych. (Źródło ilustracji: Microchip Technology)

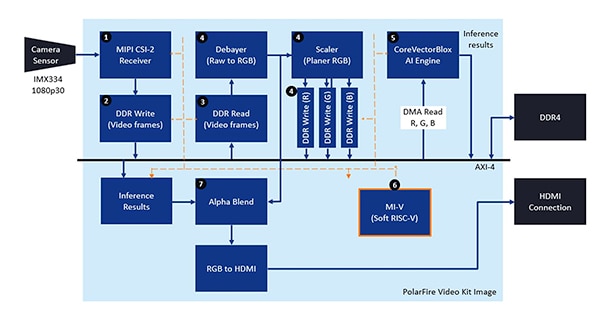

Zestaw jest dostarczany z kompletnym projektem Libero służącym do generowania plików oprogramowania układowego i obiektu BLOB sieci. Po zaprogramowaniu plików obiektu BLOB w wewnętrznej pamięci flash deweloper może kliknąć przycisk Run w projekcie Libero, aby uruchomić przykładowe zastosowanie, które przetwarza obrazy wideo z czujnika kamery i przedstawia wyniki wnioskowania na wyświetlaczu (ilustracja 10).

Ilustracja 10: zestaw do przetwarzania wideo i obrazów za pomocą macierzy bramek PolarFire FPGA firmy Microchip Technology przedstawia, w jaki sposób można zaprojektować i skorzystać z wdrożenia inteligentnego, wbudowanego systemu przetwarzania danych wizyjnych w macierzach bramek FPGA wykorzystujących aparat sieci neuronowych CoreVectorBlox firmy Microchip. (Źródło ilustracji: Microchip Technology)

Ilustracja 10: zestaw do przetwarzania wideo i obrazów za pomocą macierzy bramek PolarFire FPGA firmy Microchip Technology przedstawia, w jaki sposób można zaprojektować i skorzystać z wdrożenia inteligentnego, wbudowanego systemu przetwarzania danych wizyjnych w macierzach bramek FPGA wykorzystujących aparat sieci neuronowych CoreVectorBlox firmy Microchip. (Źródło ilustracji: Microchip Technology)

Dla każdego wejściowego kadru wideo system wykonuje następujące czynności na bazie macierzy bramek FPGA (numeracja pokrywa się z ilustracją 10):

- ładowanie kadru z kamery

- zapis kadru w pamięci RAM

- odczyt kadru z pamięci RAM

- przetwarzanie surowego obrazu na RGB, do formatu planer RGB i zapis wyniku w pamięci RAM

- Procesor Mi-V RISC-V z miękkim rdzeniem uruchamia aparat CoreVectorBlox, który pobiera obraz z pamięci RAM, wykonuje wnioskowanie i zapisuje wyniki prawdopodobieństwa klasyfikacji z powrotem w pamięci RAM

- Procesor Mi-V wykorzystuje wyniki do utworzenia kadru nakładki z obwiedniami, wynikami klasyfikacji i innymi metadanymi i zapisuje kadr w pamięci RAM

- Oryginalny kadr zostaje połączony z nakładką i przesłany na wyświetlacz HDMI

Przykładowe zastosowanie obsługuje akcelerację dostępną w modelach Tiny Yolo V3 i MobileNet V2, jednak deweloperzy mogą uruchamiać inne modele obsługiwane przez zestaw SDK, wykorzystując metody opisane wcześniej, wprowadzając niewielką zmianę w kodzie, aby dodać nazwę modelu i metadane do istniejącej listy, zawierającej dwa domyślne modele.

Podsumowanie

Algorytmy sztucznej inteligencji, takie jak modele sieci neuronowych zazwyczaj nakładają duże obciążenia obliczeniowe, które wymagają bardziej wydajnych zasobów obliczeniowych od takich, które są dostępne w przypadku procesorów ogólnego przeznaczenia. Chociaż macierze bramek FPGA są dobrze przygotowane, aby sprostać wymaganiom wydajności i niskiego zapotrzebowania energetycznego przy wykonywaniu modelu wnioskowania, konwencjonalne metody opracowywania FPGA mogą wydawać się skomplikowane, często powodując, że deweloperzy zwracają się ku nie w pełni optymalnym rozwiązaniom.

Używając wyspecjalizowanych, zastrzeżonych metod i oprogramowania firmy Microchip Technology, deweloperzy bez doświadczenia z macierzami bramek FPGA mogą wdrażać projekty oparte na wnioskowaniu, lepiej spełniające wymagania dotyczące wydajności, zużycia energii, jak również harmonogramu projektowania.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.