Wdrażanie energooszczędnych (o niskiej mocy), wysokowydajnych systemów przetwarzania brzegowego z wykorzystaniem macierzy FPGA w technologii Quantum firmy Efinix

Przekazane przez: Północnoamerykańscy redaktorzy DigiKey

2020-03-17

W klasycznych systemach przetwarzania w chmurze występują problemy z opóźnieniami, bezpieczeństwem danych, ochroną prywatności użytkowników końcowych, dostępną przepustowością i niezawodnością łączności. Aby im zapobiegać, projektanci i architekci systemów skłaniają się coraz częściej do stosowania systemów przetwarzania brzegowego. Systemy przetwarzania brzegowego stwarzają jednak pewne wyzwania, począwszy od kosztów, rozmiarów, wydajności i zużycia energii, a skończywszy na zagadnieniach związanych ze skalowalnością, elastycznością i możliwością ich rozbudowy. Dzieje się tak zwłaszcza wtedy, gdy projektanci starają się przeprowadzać więcej operacji przetwarzania obrazu i wdrażać więcej systemów sztucznej inteligencji (AI) oraz algorytmów uczenia maszynowego (ML) bliżej źródła danych.

W rezultacie przestają korzystać z tradycyjnych mikrokontrolerów (MCU) lub procesorów aplikacji (AP), a zaczynają brać pod uwagę bezpośrednio programowalne macierze bramek (FPGA), które umożliwiają równoległe przetwarzanie danych. Ciągłe udoskonalenia w zakresie projektowania i wdrażania macierzy FPGA sprawiają, że mogą one spełnić wiele tych wymagań albo nawet wszystkie z nich - jako samodzielne urządzenia albo w połączeniu z MCU i AP. Wielu projektantów nie ma jednak wystarczającej wiedzy na temat macierzy FPGA i obawia się, że przyswojenie jej będzie zbyt trudne.

W tym artykule krótko omówiono proces przejścia z systemów przetwarzania w chmurze do systemów przetwarzania brzegowego i wyjaśniono, dlaczego tradycyjne architektury przetwarzania nie sprawdzają się w projektach związanych z przetwarzaniem obrazów, AI czy ML. Przedstawiono tu najważniejsze informacje na temat macierzy FPGA oraz pokazano ich architektoniczną przewagę w zastosowaniach brzegowych wymagających przetwarzania dużej ilości danych. Zaprezentowano także nowe podejście do macierzy FPGA - technologię Quantum firmy Efinix - i opisano proces jej wdrożenia.

Dlaczego warto wybrać systemy przetwarzania brzegowego?

W tradycyjnych systemach przetwarzania w chmurze dane są zbierane z wielu, często odległych miejsc, a następnie przekazywane do działającego w chmurze systemu do przechowywania i analizy danych. Takie podejście ma jednak wiele wad. Należą do nich koszty przesyłania dużych ilości nieprzetworzonych („surowych”) danych, konieczność utrzymania integralności i zapewnienia bezpieczeństwa tych danych podczas transferu, opóźnienia w reagowaniu, problemy z ochroną prywatności użytkowników końcowych, a także często zawodne połączenia z internetem i nieoptymalne wykorzystanie dostępnej przepustowości.

Jak sama nazwa wskazuje, wykorzystanie systemu przetwarzania brzegowego wiąże się z przeniesieniem przetwarzania i analizy bliżej krawędzi sieci, czyli bezpośrednio w miejsce, gdzie dane są generowane, analizowane, gromadzone i wykorzystywane. Pojęcie „system przetwarzania brzegowego” nie odnosi się do żadnych konkretnych aplikacji ani urządzeń. Projektanci mogą - w zależności od potrzeb - wybrać przetwarzanie danych tylko na krawędzi sieci lub zdecydować się na zachowanie równowagi między przetwarzaniem brzegowym a przetwarzaniem w chmurze.

Z systemów przetwarzania brzegowego korzystają między innymi inteligentne fabryki, inteligentne miasta, inteligentne domy i inteligentny transport. Urządzeniami brzegowymi mogą być zarówno duże, wysokiej klasy serwery brzegowe, jak i stosunkowo małe systemy czujników i aktuatorów zlokalizowanych na brzegu Internetu, czyli w punkcie generowania danych.

Zalety macierzy FPGA

Tradycyjne procesory przetwarzają dane bardzo wydajnie, jeśli chodzi o procesy podejmowania decyzji i zadania sekwencyjne. Wydajność ta jednak dramatycznie spada przy zastosowaniu wielu algorytmów przetwarzania danych, takich jak algorytmy stosowane w systemach przetwarzania obrazu, sztucznej inteligencji czy uczenia maszynowego. Zadania te często można podzielić na masowo równoległe (w odróżnieniu od sekwencyjnych) potoki przetwarzania danych. To właśnie takie zastosowania są przenoszone nawet na (często skrajne) krawędzie sieci.

Fakt, że macierze FPGA można zaprogramować (skonfigurować) pod kątem wdrożenia dowolnej kombinacji funkcji, pozwala na masowo równoległe wykonywanie na nich algorytmów przetwarzania obrazu, AI i ML, minimalizując w ten sposób opóźnienia przy jednoczesnym zmniejszeniu zużycia energii. Oprócz głównej programowalnej struktury macierze FPGA są też wyposażone w bloki cyfrowego przetwarzania sygnałów (DSP) zawierające specjalne multiplikatory, które znacznie przyspieszają operacje intensywnie wykorzystujące DSP. Macierze FPGA mają też wbudowane w układy scalone (tzw. on-chip) bloki pamięci, które ułatwiają przetwarzanie danych bezpośrednio w takim układzie scalonym, co jest znacznie szybsze niż inne rozwiązania.

Na rynku działa wielu sprzedawców macierzy FPGA, a każdy z nich ma własną, unikatową ofertę. Jeden z nich, firma Efinix, opracował specjalną architekturę macierzy FPGA o nazwie Quantum, optymalnie dostosowaną do systemów przetwarzania brzegowego, a w szczególności do przetwarzania obrazów. Na bazie tej technologii firma opracowała serię macierzy FPGA Trion (oraz specjalizowane układy scalone Quantum ASIC), charakteryzujące się wskaźnikiem PPA (moc-wydajność-powierzchnia) 4 razy lepszym niż tradycyjne technologie macierzy FPGA (ilustracja 1). Układy FPGA i ASIC łączy zintegrowane środowisko rozwojowe (IDE) Efinity.

Ilustracja 1: macierze FPGA Trion dzięki swojej wydajności (PPA) sprawdzają się w zastosowaniach takich jak niestandardowe układy logiczne, przyspieszanie obliczeń, ML, uczenie głębokie (deep learning) i przetwarzanie obrazu. Dzięki środowisku (IDE) Efinity użytkownicy mogą płynnie przejść z macierzy FPGA Trion do układów Quantum ASIC stosowanych w produkcji wysokonakładowej. (Źródło ilustracji: Efinix)

Ilustracja 1: macierze FPGA Trion dzięki swojej wydajności (PPA) sprawdzają się w zastosowaniach takich jak niestandardowe układy logiczne, przyspieszanie obliczeń, ML, uczenie głębokie (deep learning) i przetwarzanie obrazu. Dzięki środowisku (IDE) Efinity użytkownicy mogą płynnie przejść z macierzy FPGA Trion do układów Quantum ASIC stosowanych w produkcji wysokonakładowej. (Źródło ilustracji: Efinix)

Czym jest technologia Quantum?

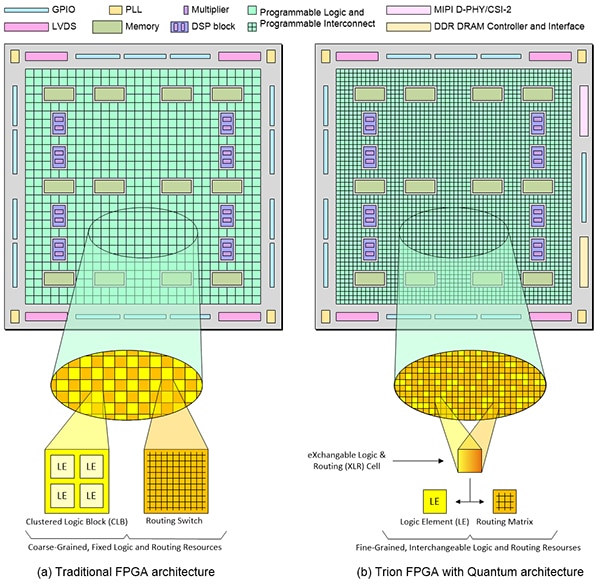

Podobnie jak tradycyjne macierze FPGA, macierze FPGA Trion zawierają bloki pamięci i DSP. Różnica leży w ich programowalnej strukturze (ilustracja 2). Kluczową częścią logiki programowalnej jest element logiczny (LE). Każdy element logiczny zawiera tablicę podglądu (LUT), multiplekser i rejestr, które można skonfigurować zgodnie z wymaganiami. Strukturę programowalną tradycyjnych macierzy FPGA można opisać jako „gruboziarnistą”.

Ilustracja 2: tradycyjna architektura FPGA (a) jest „gruboziarnista” i choć jej logika i połączenia są programowalne, to nadal są to zasoby stałe. Macierze FPGA Trion (b) oparte na architekturze Quantum są natomiast „drobnoziarniste”, a ich logika i zasoby routingu są wymienne (Źródło ilustracji: Max Maxfield)

Ilustracja 2: tradycyjna architektura FPGA (a) jest „gruboziarnista” i choć jej logika i połączenia są programowalne, to nadal są to zasoby stałe. Macierze FPGA Trion (b) oparte na architekturze Quantum są natomiast „drobnoziarniste”, a ich logika i zasoby routingu są wymienne (Źródło ilustracji: Max Maxfield)

W „gruboziarnistych” strukturach wiele elementów logicznych jest zbieranych razem w większy, podzielony na klastry blok logiczny (clustered logic block, CLB). Warto tu zauważyć, że niektórzy sprzedawcy używają terminu „konfigurowalny blok logiczny” (configurable logic block, CLB), inni natomiast określenia „blok matrycowy” (logic array block, LAB), ale oznaczają one to samo.

Należy pamiętać, że ta ilustracja ma charakter ideowy. Bloki CLB i przełączniki routingu (programowalne połączenia) w tradycyjnych macierzach FPGA tak naprawdę nie mają formy szachownicy. Są jednak stałe i niezmienne w tym sensie, że układy logiki programowalnej zawsze będą układami logiki programowalnej, a połączenia programowalne zawsze będą połączeniami programowalnymi.

W porównaniu do tradycyjnych architektur macierze FPGA Trion mają znacznie bardziej drobnoziarnistą strukturę: aż do poziomu pojedynczego elementu logicznego. Każda komórka XLR (exchangeable logic and routing cell) może ponadto pracować zarówno jako element logiczny, jak i jako część macierzy routingu.

Komórki konfiguracyjne wykorzystywane w architekturze Quantum wykorzystują pamięć SRAM, dzięki czemu technologia ta jest niezależna od zastosowanych układów scalonych. Mogą one być wytwarzane w dowolnej standardowej technologii CMOS bez konieczności stosowania specjalnych etapów obróbki, niezbędnych podczas produkcji alternatywnych technologii konfiguracji, takich jak flash i antifuse, stosowanych w niektórych macierzach FPGA.

To właśnie logika i routing konfigurowalne programowo oraz wysoko wydajna adaptacyjna sieć połączeń gwarantują czterokrotną poprawę efektywności PPA (power-perfomance-area) w porównaniu z tradycyjnymi macierzami FPGA opartymi na pamięci SRAM, tworzonymi w tym samym węźle technologicznym.

Macierze FPGA wykorzystujące architekturę Quantum wymagają ponadto tylko siedmiu warstw metalizacji, w odróżnieniu do ponad 12 koniecznych w tradycyjnych macierzach FPGA. Ponieważ każda dodatkowa warstwa metalu wymaga wielu etapów maskowania i obróbki, zastosowanie tylko siedmiu warstw zmniejsza koszty projektowania i produkcji oraz zwiększa wydajność.

Wszystkie te cechy i funkcje są bardzo użyteczne dla projektantów szukających korzyści w zakresie kosztów, rozmiaru, wydajności i elastyczności systemów przetwarzania brzegowego i przetwarzania obrazu. Macierze FPGA Trion idealnie sprawdzają się więc zarówno w tradycyjnych zastosowaniach, jak i w nowo powstających zastosowaniach z zakresu przetwarzania brzegowego i przetwarzania obrazu. Te ostatnie obejmują telefonię komórkową, Internet rzeczy (IoT), automatykę, robotykę, fuzję sensorów, systemy wizyjne, sztuczną inteligencję (AI) oraz uczenie maszynowe (ML).

Struktura macierzy FPGA Trion

Macierze FPGA Trion wytwarzane są jako układy o niskiej mocy w technologii 40 nanometrów (nm). Liczba zastosowanych w nich elementów logicznych waha się od czterech do dwustu tysięcy, choć proces ten można skalować w celu produkcji znacznie większych urządzeń. Wszystkie macierze FPGA Trion zawierają bloki pamięci i DSP, ale ich pojemność i liczba różnią się w zależności od wielkości urządzenia. Mniejsze urządzenia, takie jak T4F81C2, oferują mniej funkcji (tj. 3888 elementów logicznych, 78848 bitów pamięci, 59 GPIO) i są przeznaczone do ręcznych platform sterowania.

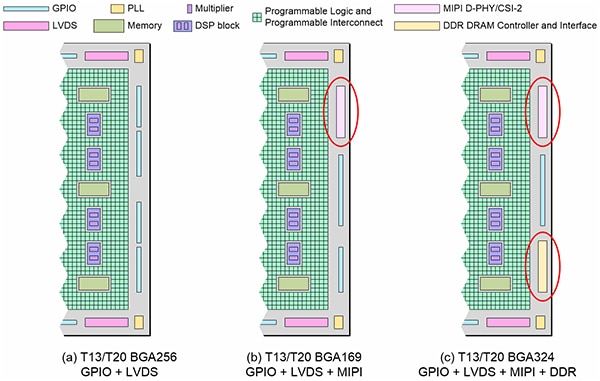

Urządzenia wyższej klasy, takie jak T20F256C3, zawierają odpowiednio więcej zasobów (tj. 19728 elementów logicznych, 1069548 bitów pamięci, 195 GPIO). Urządzenie T13F256C3 jest podobne do T20F256C3, ale zawiera 12828 elementów logicznych. Urządzenia takie jak T13/T20 występują ponadto w różnych wersjach (ilustracja 3).

Ilustracja 3: modele T13/T20 BGA256 firmy Efinix (a) to generyczne macierze FPGA, które będą idealnym wyborem w przypadku projektów wymagających dużej liczby operacji na wejściach-wyjściach. Modele T13/T20 BGA169 (b) zawierają dwa bloki z rdzeniem twardym MIPI D-PHY/CSI-2 i nadają się do projektów wymagających obsługi interfejsu MIPI kamery. Modele T13/T20 BGA324 (c) uzupełniają interfejsy MIPI o zaimplementowany w twardym rdzeniu kontroler i interfejs pamięci x16-bit DRAM DDR, odpowiedni do projektów wymagających dużej przepustowości pamięci. (Źródło ilustracji: Max Maxfield)

Ilustracja 3: modele T13/T20 BGA256 firmy Efinix (a) to generyczne macierze FPGA, które będą idealnym wyborem w przypadku projektów wymagających dużej liczby operacji na wejściach-wyjściach. Modele T13/T20 BGA169 (b) zawierają dwa bloki z rdzeniem twardym MIPI D-PHY/CSI-2 i nadają się do projektów wymagających obsługi interfejsu MIPI kamery. Modele T13/T20 BGA324 (c) uzupełniają interfejsy MIPI o zaimplementowany w twardym rdzeniu kontroler i interfejs pamięci x16-bit DRAM DDR, odpowiedni do projektów wymagających dużej przepustowości pamięci. (Źródło ilustracji: Max Maxfield)

MIPI CSI-2 jest interfejsem kamery najpowszechniej stosowanym w urządzeniach przenośnych i w innych zastosowaniach ze względu na niską moc (małe zużycie energii), niewielkie opóźnienia i tanią łączność typu chip-to-chip. Obsługuje również szeroki zakres formatów zapewniających wysoką jakość obrazu, w tym 1080p, 4K, 8K (i wyższe), a także obrazowanie w wysokiej rozdzielczości. Szczególnie interesujący jest fakt, że MIPI CSI-2 jest interfejsem wykorzystywanym najczęściej przez czujniki wizyjne w zastosowaniach związanych z przetwarzaniem brzegowym. Macierze FPGA T13/T20 BGA169 sprawdzają się w tego typu projektach wyjątkowo dobrze dzięki dwóm blokom z rdzeniem twardym obsługującym MIPI D-PHY/CSI-2 (ilustracja 3).

Pamięć DDR obsługuje transfery danych o dużej przepustowości, ale wymaga również przestrzegania ścisłego protokołu taktowania. Oprócz interfejsów MIPI D-PHY/CSI-2 macierze Trion T13/T20 BGA324 (ilustracja 3) zawierają także zabezpieczony interfejs pamięci x16-bit DDR DRAM oraz sterownik do projektów wymagających dużej przepustowości.

Macierze Quantum ASIC

Jak już wcześniej zauważono, komórki konfiguracyjne używane w macierzach FPGA Trion wykorzystują pamięć SRAM. Dlatego przy pierwszym uruchomieniu systemu konieczne jest wczytanie danych konfiguracyjnych macierzy FPGA Trion z zewnętrznej pamięci albo poprzez przesyłanie bitów (bit-banging) przez procesor-host. Aby było to możliwe w produkcji wysokonakładowej, firma Efinix oferuje również rozwiązania Quantum Accelerated embedded FPGA (eFPGA) w postaci układów Quantum ASIC. W tym przypadku firma Efinix może na podstawie konstrukcji T4, T8, T13 lub T20 stworzyć zaprogramowane wersje układu Quantum ASIC, uruchamiające się bez konieczności stosowania zewnętrznego urządzenia konfiguracyjnego.

Projektowanie i prace rozwojowe przy użyciu macierzy FPGA Trion

Firma Efinix oferuje różnorodne płytki ewaluacyjne i zestawy rozwojowe, które umożliwiają użytkownikom zapoznanie się z możliwościami macierzy FPGA Trion. Należą do nich zestaw rozwojowy Trion T8F81C-DK T8 do macierzy FPGA Trion, płytka ewaluacyjna Trion T20F256C-DK T20 macierzy FPGA Trion oraz zestaw rozwojowy Trion T20MIPI-DK T20 MIPI D-PHY/CSI-2.

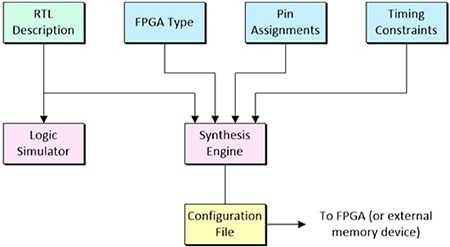

Jedną z technik wykorzystywanych najczęściej do programowania macierzy FPGA jest programowanie zgodne z metodyką LDD (language-driven design). Wymaga to określenia celu projektu na poziomie ideowym (tzw. register transfer level, RTL) przy użyciu języka opisu sprzętu (hardware description language, HDL), takiego jak Verilog lub VHDL. Po weryfikacji za pomocą symulacji logicznej koncepcję tę przekazuje się do mechanizmu syntezy logicznej wraz z dodatkowymi informacjami, takimi jak docelowy typ macierzy FPGA, przyporządkowanie pinów i ograniczenia czasowe (np. maksymalne opóźnienie wejścia do wyjścia). Mechanizm syntezy generuje plik konfiguracyjny, który jest wczytywany bezpośrednio do macierzy FPGA albo do pamięci zewnętrznej (ilustracja 4).

Ilustracja 4: po weryfikacji poprzez symulację logiczną, opis projektu w RTL jest przekazywany do silnika syntezy wraz z dodatkowymi informacjami na temat projektu, takimi jak rodzaj macierzy FPGA, przyporządkowanie wtyków i ograniczenia czasowe. Mechanizm syntezy generuje plik konfiguracyjny, który jest wczytywany bezpośrednio do macierzy FPGA. (Źródło ilustracji: Max Maxfield)

Ilustracja 4: po weryfikacji poprzez symulację logiczną, opis projektu w RTL jest przekazywany do silnika syntezy wraz z dodatkowymi informacjami na temat projektu, takimi jak rodzaj macierzy FPGA, przyporządkowanie wtyków i ograniczenia czasowe. Mechanizm syntezy generuje plik konfiguracyjny, który jest wczytywany bezpośrednio do macierzy FPGA. (Źródło ilustracji: Max Maxfield)

Opracowane przez firmę Efinix zintegrowane środowisko rozwojowe (IDE) Efinity należy do tej właśnie klasy narzędzi. Oprogramowanie to zapewnia pełną translację do poziomu RTL do strumienia bitów, ma prosty, łatwy w użyciu graficzny interfejs użytkownika (GUI) i umożliwia uruchamianie skryptów z linii poleceń. Intuicyjny pulpit prowadzi dewelopera przez kolejne etapy (tj. syntezę, rozmieszczenie elementów, definiowanie połączeń między nimi i generowanie strumienia bitów), a każdy z nich można kontrolować automatycznie lub ręcznie. Deweloperzy mogą zastosować mechanizm syntezy Efinity, aby w pełni wykorzystać możliwości architektury Quantum w macierzach FPGA Trion do tworzenia urządzeń z czterokrotnie większym wskaźnikiem PPA.

Oprócz obsługi przepływów symulacyjnych przy użyciu ModelSim, NCSim lub bezpłatnych symulatorów IVerilog, IDE Efinity oferuje również moduły Interface Designer (do ograniczania logiki i przypisywania wtyków do bloków na peryferiach urządzenia), Floorplan Editor (do przeglądania logiki projektu i rozmieszczania elementów oraz określania połączeń między nimi), Timing Browser i statyczną analizę taktowania (do pomiaru wydajności projektu) oraz zintegrowany debugger sprzętowy z analizatorem logicznym i wirtualnymi rdzeniami debugującymi wejścia-wyjścia.

Podsumowanie

Gdy coraz więcej operacji obliczeniowych związanych z przetwarzaniem obrazu, AI i ML przeprowadza się na krawędzi sieci, a nie w chmurze, projektanci muszą rozważyć zastosowanie w architekturze systemów przetwarzania macierzy FPGA - pomaga to radzić sobie z kwestiami takimi jak koszty, wydajność, zużycie energii, rozmiar, skalowalność, elastyczność i możliwość rozbudowy systemu.

Może to czasem wymagać od projektantów poszerzenia wiedzy i zdobycia nowych umiejętności, ale rozwój technologiczny w dziedzinie macierzy FPGA (takich jak układy Quantum firmy Efinix) sprawi, że inwestycja ta szybko się opłaci: pozwoli obniżyć koszty, zmniejszyć rozmiary urządzeń, osiągnąć wyższą wydajność i większą uniwersalność.

W rezultacie macierze FPGA idealnie sprawdzają się zarówno w tradycyjnych zastosowaniach, jak i w nowatorskich systemach przetwarzania brzegowego wykorzystywanych w sektorach telefonii komórkowej, IoT, automatyki, robotyki, fuzji sensorów, systemów wizyjnych, AI i ML.

Dodatkowe zasoby

- Fundamentals: The IoT, IIoT, AIoT, and Why They’re the Future of Industrial Automation (Podstawy: IoT, IIoT, AIoT i dlaczego jest to przyszłość automatyki przemysłowej)

- Fundamentals of FPGAs: What Are FPGAs and Why Are They Needed? (Podstawy macierzy FPGA: czym są macierze FPGA i do czego służą?)

- Fundamentals of FPGAs – Part 2: Getting Started with Lattice Semiconductor’s FPGAs (Podstawy macierzy FPGA – część 2: pierwsze kroki z macierzami FPGA firmy Lattice Semiconductor)

- Fundamentals of FPGAs – Part 3: Getting Started with Microchip Technology’s FPGAs (Podstawy macierzy FPGA – część 3: pierwsze kroki z macierzami FPGA firmy Microchip Technology)

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.