Przeznaczenie i sposób używania bezpośrednio programowalnych macierzy bramek (FPGA) firmy Efinix do obrazowania AI/ML – część 1: pierwsze kroki

Przekazane przez: DigiKey's European Editors

2023-04-20

Uwaga od redakcji: nowe podejścia do architektur bezpośrednio programowalnych macierzy bramek (FPGA) zwiększają kontrolę i elastyczność, pozwalając na sprostanie potrzebom uczenia maszynowego (ML) i sztucznej inteligencji (AI). Część 1 tej dwuczęściowej serii przedstawia przykład takiej architektury firmy Efinix oraz sposób rozpoczęcia z nią pracy przy użyciu płytki rozwojowej. W części 2 omówiono sposób podłączenia płytki rozwojowej do urządzeń zewnętrznych i peryferyjnych, takich jak kamera.

Macierze FPGA odgrywają kluczową rolę w wielu zastosowaniach, od kontroli przemysłowej i bezpieczeństwa po robotykę, lotnictwo i motoryzację. Dzięki elastycznej charakterystyce programowalnego rdzenia logicznego i jego szerokim możliwościom współpracy, jednym z rozwijających się zastosowań macierzy FPGA jest przetwarzanie obrazu, w którym ma być zastosowane wnioskowanie z użyciem uczenia maszynowego (ML). Macierze FPGA doskonale sprawdzają się we wdrażaniu rozwiązań zawierających kilka szybkich interfejsów kamer. Ponadto macierze FPGA umożliwiają implementację dedykowanych potoków przetwarzania w układach logicznych, eliminując w ten sposób wąskie gardła związane z rozwiązaniami opartymi na procesorach (CPU) lub procesorach graficznych (GPU).

Dla wielu deweloperów ich aplikacje wymagają jednak większej funkcjonalności uczenia maszynowego i sztucznej inteligencji (ML/AI) oraz dokładniejszej kontroli lub routingu i logiki, co wykracza poza możliwości klasycznych architektur bezpośrednio programowalnych macierzy bramek (FPGA) z kombinatorycznymi blokami logicznymi (CLB). Nowsze podejścia do architektur FPGA rozwiązują te problemy. Na przykład architektura Quantum firmy Efinix wykorzystuje blok eXchangeable Logic and Routing (XLR).

W niniejszym artykule omówiono kluczowe funkcje i cechy architektury FPGA firmy Efinix, jej możliwości w zakresie sztucznej inteligencji i uczenia maszynowego (AI/ML) oraz rzeczywiste implementacje. Następnie omówiono płytkę rozwojową i związane z nią narzędzia, które deweloperzy mogą wykorzystywać do szybkiego rozpoczęcia prac nad kolejnym projektem obrazowania z użyciem sztucznej inteligencji i uczenia maszynowego (AI/ML).

Urządzenia FPGA firmy Efinix

Firma Efinix oferuje obecnie dwie gamy urządzeń. Na początku firma wprowadziła grupę Trion, która oferuje gęstości elementów logicznych (LE) od 4000 (4K) do 120K, która jest wytwarzana z wykorzystaniem procesu SMIC 40LL. Najnowsza linia urządzeń Titanium oferuje gęstość elementów logicznych od 35K do 1 miliona (1M) i jest wytwarzana na bardzo popularnym węźle 16nm TSMC.

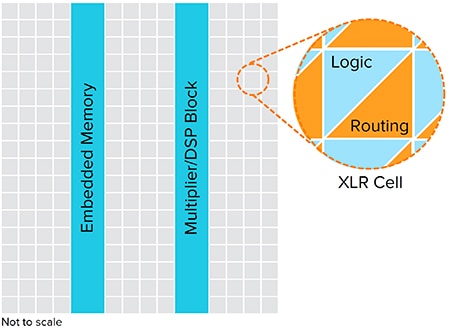

Oba produkty są oparte na architekturze Quantum - unikalnej w świecie macierzy FPGA. Standardowa architektura FPGA bazuje na blokach CLB, które na najprostszym poziomie zawierają tablicowanie (LUT) i przerzutniki flip-flop. Bloki CLB implementują równania logiczne, które następnie są połączone ze sobą poprzez routing. Architektura Quantum firmy Efinix odchodzi od odrębnych bloków logicznych i routingowych dzięki blokowi XLR.

Blok XLR jest wyjątkowy, ponieważ może być skonfigurowany jako komórka logiczna z tablicowaniem (LUT), rejestr i sumator lub matryca routingu. Takie podejście oferuje bardziej rozdrobnioną architekturę zapewniającą elastyczność routingu, umożliwiając implementacje mocno obciążone logiką lub routingiem, w celu osiągnięcia żądanej wydajności.

Ilustracja 1: blok XLR jest wyjątkowy, ponieważ może być skonfigurowany jako komórka logiczna z tablicowaniem (LUT), rejestr i sumator lub matryca routingu. (Źródło ilustracji: Efinix)

Ilustracja 1: blok XLR jest wyjątkowy, ponieważ może być skonfigurowany jako komórka logiczna z tablicowaniem (LUT), rejestr i sumator lub matryca routingu. (Źródło ilustracji: Efinix)

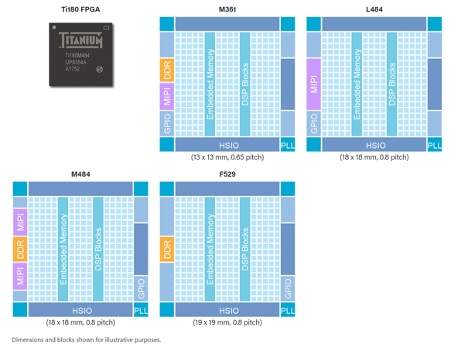

Najnowsza grupa urządzeń Titanium oferuje deweloperom najbardziej zaawansowane funkcje (ilustracja 2). Oprócz rdzenia XLR, zapewnia wielogigabitowe łącza szeregowe działające z szybkością 16Gbps lub 25,8Gbps, w zależności od wybranego urządzenia. Wspomniane łącza są kluczowe dla szybkiej wymiany danych z mikroukładem.

Ilustracja 2: bezpośrednio programowalne macierze bramek (FPGA) Titanium Ti180 są dostępne w różnych wersjach w zależności od szerokości magistrali, wymagań dotyczących wejść-wyjść i pamięci. (Źródło ilustracji: Efinix)

Ilustracja 2: bezpośrednio programowalne macierze bramek (FPGA) Titanium Ti180 są dostępne w różnych wersjach w zależności od szerokości magistrali, wymagań dotyczących wejść-wyjść i pamięci. (Źródło ilustracji: Efinix)

Urządzenia Titanium oferują również szeroki zakres możliwości stosowania interfejsów wejścia-wyjścia (I/O), które można pogrupować jako wejścia-wyjścia ogólnego przeznaczenia (GPIO) mogące obsługiwać standardy wejść-wyjść jednostronnych, takie jak niskonapięciowe komplementarne półprzewodniki tlenkowe (LVCMOS) przy napięciu 3,3V, 2,5V i 1,8V.

W przypadku interfejsów różnicowych i interfejsów o dużej szybkości, urządzenia Titanium zapewniają szybkie wejścia-wyjścia (HSIO), które obsługują standardy wejść-wyjść jednostronnych, takie jak LVCMOS na napięcia 1,2V, 1,5V oraz SSTL i HSTL. Standardy wejść-wyjść różnicowych obsługiwane przez HSIO obejmują niskonapięciowe sygnały różnicowe (LVDS), różnicowe SSTL i HSTL.

Nowoczesne bezpośrednio programowalne macierze bramek (FPGA) wymagają również pamięci ściśle przyległej o dużej przepustowości, która jest wykorzystywana do przechowywania ramek obrazu w aplikacjach przetwarzania obrazu, danych próbkowanych w przetwarzaniu sygnału oraz oczywiście do uruchamiania systemów operacyjnych i oprogramowania dla procesorów zaimplementowanych w macierzach FPGA. Urządzenia z serii Titanium mogą współpracować z urządzeniami, w których wykorzystano technologię DDR4 (Dynamic Data Rate Four) i DDR4(x) (LPDDR4(x)) niskiej mocy. W zależności od urządzenia Titanium obsługiwane są szerokości magistrali x32 (J) lub x16 (M), jednak niektóre urządzenia nie obsługują LPDDR4 (L).

Macierze FPGA Titanium są oparte na statycznej pamięci o dostępie swobodnym (SRAM) i wymagają pamięci konfiguracyjnej, przy czym konfiguracja urządzenia odbywa się za pomocą interfejsu JTAG lub SPI (Serial Peripheral Interconnect) typu master/slave. Aby zapewnić bezpieczeństwo tej metody konfiguracji, w macierzach FPGA Titanium wykorzystano szyfrowanie strumienia bitowego AES GCM wraz z AES GCM i algorytmem RSA-4096 służącymi do uwierzytelnienia strumienia bitowego. Silne zabezpieczenia tego typu są wymagane ze względu na lokalizację macierzy FPGA na obrzeżach, gdzie niepowołane osoby mogą uzyskać do nich dostęp i manipulować ich działaniem.

Wprowadzenie do płytek rozwojowych

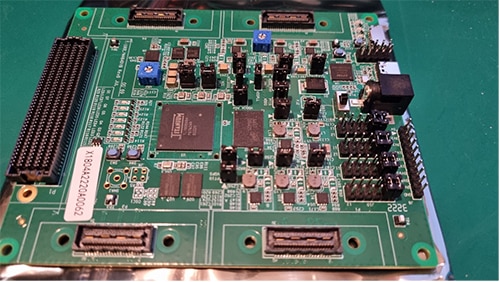

Płytki rozwojowe stanowią kluczowy element w procesie oceny macierzy FPGA, ponieważ mogą być wykorzystywane do badania możliwości urządzenia i prototypowania zastosowań, pomagając w zmniejszeniu ogólnych zagrożeń. Pierwszą płytką rozwojową dostępną do ewaluacji macierzy FPGA Titanium i rozpoczęcia prototypowania zastosowań jest Ti180 M484 (ilustracja 3). Na płytce znajduje się złącze FPGA Mezzanine Card (FMC) oraz cztery złącza QSE firmy Samtec.

Ilustracja 3: oprócz macierzy FPGA Titanium, zestaw rozwojowy Ti180 M484 zawiera złącze FMC i cztery złącza QSE firmy Samtec. (Źródło ilustracji: Adam Taylor)

Ilustracja 3: oprócz macierzy FPGA Titanium, zestaw rozwojowy Ti180 M484 zawiera złącze FMC i cztery złącza QSE firmy Samtec. (Źródło ilustracji: Adam Taylor)

Macierz FPGA Ti180 zamontowana na tej płytce rozwojowej posiada 172 tys. komórek XLR, 32 globalne zegary, 640 elementów cyfrowego przetwarzania sygnału (DSP) oraz wbudowaną pamięć RAM 13Mb. Elementy DSP umożliwiają implementację mnożenia stałoprzecinkowego 18 x 19 oraz mnożenia 48-bitowego. Mogą być również zoptymalizowane pod kątem operacji na podstawie architektury SIMD (Single Instruction, Multiple Data) działających w podwójnej lub poczwórnej konfiguracji. Elementy DSP mogą też być skonfigurowane do wykonywania operacji zmiennoprzecinkowych.

Podobnie jak większość płytek rozwojowych, model Ti180 zawiera proste diody LED i przyciski. Jego prawdziwa moc tkwi jednak w możliwościach współpracy. Płytka rozwojowa Ti180 zawiera złącze FMC o małej liczbie wtyków umożliwiające podłączenie wielu rodzajów urządzeń peryferyjnych. Jest to szeroko stosowany standard, dlatego istnieje wiele kart FMC, które umożliwiają podłączenie szybkich przetworników analogowo-cyfrowych (ADC) i cyfrowo-analogowych (DAC), sieciowanie oraz stosowanie rozwiązań pamięci i składowania danych.

Oprócz złącza FMC na płytce znajdują się cztery złącza QSE firmy Samtec umożliwiające deweloperom dodawanie kart rozszerzeń. Złącza QSE zawierają wejścia i wyjścia MIPI, przy czym każde złącze zapewnia albo wejście, albo wyjście MIPI.

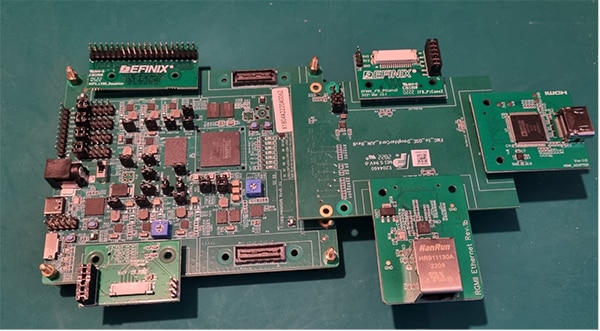

Ilustracja 4: zestaw rozwojowy Ti180 M484 z wszechstronnymi możliwościami rozszerzeń opartych na złączach QSE i FMC. (Źródło ilustracji: Adam Taylor)

Ilustracja 4: zestaw rozwojowy Ti180 M484 z wszechstronnymi możliwościami rozszerzeń opartych na złączach QSE i FMC. (Źródło ilustracji: Adam Taylor)

Płytka Ti180 zawiera również 256Mb LPDDR4 do obsługi wysokowydajnej pamięci wymaganej w przetwarzaniu obrazu lub sygnału. Ponadto płytka rozwojowa zapewnia wiele opcji taktowania z częstotliwością 25, 33,33, 50 i 74,25MHz, które można stosować z pętlą synchronizacji fazowej (PLL) urządzenia do generowania różnych częstotliwości wewnętrznych.

Możliwość przeprogramowania i debugowania na płytce podczas rozwoju ma krytyczne znaczenie i wymaga połączenia JTAG za pośrednictwem interfejsu USB-C, w który płytka jest wyposażona. Zapewnia również pamięć nieulotną w postaci dwóch urządzeń NOR typu flash 256Mb, które mogą być stosowane do demonstracji rozwiązania konfiguracyjnego.

Płytka jest zasilana przez uniwersalny zasilacz 12V wchodzący w skład zestawu. Zestaw zawiera również adapter FMC-QSE wraz z kartami rozszerzeń bazującymi na złączach QSE dla HDMI, sieci Ethernet, interfejsu mobilnego procesora przemysłowego (MIPI) i niskonapięciowego sygnału różnicowego (LVDS). Aby zademonstrować możliwości przetwarzania obrazu płytki Ti180, dostarczana jest również podwójna płytka podrzędna RPI oraz dwie karty IMX477 do kamer.

Środowisko programowe

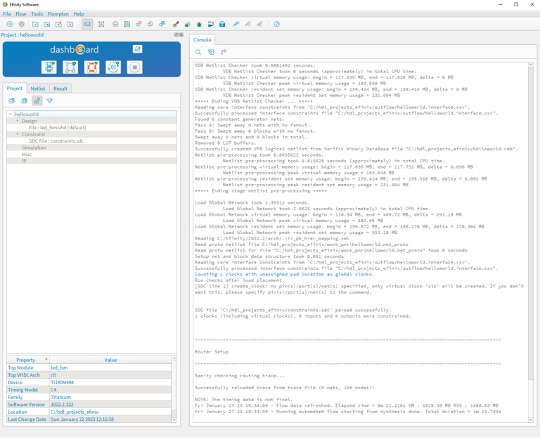

W projektach wdrożeniowych uwzględniających płytkę rozwojową Ti180, wykorzystywane jest oprogramowanie Efinity firmy Efinix. Oprogramowanie to umożliwia generowanie strumienia bitów poprzez syntezę oraz miejsce i trasę. Zapewnia również deweloperom bloki własności intelektualnej (IP), analizę taktowania i debugowanie mikroukładowe.

Należy pamiętać, że płytka rozwojowa jest niezbędna do uzyskania dostępu do oprogramowania Efinity. W odróżnieniu od innych producentów, omawiane narzędzie nie posiada różnych wersji, które wymagają dodatkowego licencjonowania.

W oprogramowaniu Efinity tworzone są nowe projekty dla wybranego urządzenia. Pliki RTL mogą być następnie dodawane do projektu oraz można tworzyć ograniczenia dla taktowania i projektu wejść-wyjść. Oprogramowanie Efinity umożliwia deweloperom implementację projektu wejść-wyjść z wykorzystaniem szybkich wejść-wyjść (HSIO), wejścia-wyjścia ogólnego przeznaczenia (GPIO) i wejścia-wyjścia specjalistyczne.

Ilustracja 5: nowe projekty dla wybranego urządzenia są tworzone w oprogramowaniu Efinity. (Źródło ilustracji: Adam Taylor)

Ilustracja 5: nowe projekty dla wybranego urządzenia są tworzone w oprogramowaniu Efinity. (Źródło ilustracji: Adam Taylor)

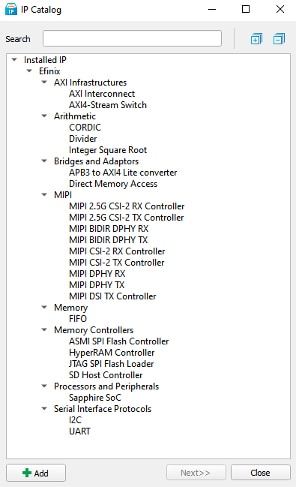

Krytycznym elementem projektu wykorzystującego bezpośrednio programowalną macierz bramek (FPGA) jest wykorzystanie własności intelektualnej (IP), zwłaszcza w przypadku złożonych pod tym względem rozwiązań, takich jak interfejsy AXI Interconnect, kontrolery pamięci i procesory typu soft-core. Oprogramowanie Efinity zapewnia deweloperom szereg bloków IP, które mogą przyspieszyć proces projektowania.

Ilustracja 6: oprogramowanie Efinity zapewnia deweloperom katalog własności intelektualnej (IP), który pozwala przyspieszyć projektowanie. (Źródło ilustracji: Adam Taylor)

Ilustracja 6: oprogramowanie Efinity zapewnia deweloperom katalog własności intelektualnej (IP), który pozwala przyspieszyć projektowanie. (Źródło ilustracji: Adam Taylor)

Chociaż macierze FPGA doskonale nadają się do implementacji struktur przetwarzania równoległego, wiele takich projektów zawiera procesory typu soft-core. Umożliwiają one implementację przetwarzania sekwencyjnego, takiego jak komunikacja sieciowa. Aby umożliwić wykorzystanie procesorów typu soft-core w urządzeniach firmy Efinix, oprogramowanie Efinity zapewnia narzędzie konfiguracyjne Sapphire układu SoC (System-on-Chip). Sapphire pozwala deweloperowi zdefiniować system wieloprocesorowy posiadający zarówno pamięci podręczne, jak i koherencję pamięci podręcznej na wielu procesorach, oraz możliwość uruchomienia zintegrowanego systemu operacyjnego Linux. W narzędziu Sapphire deweloper może wybrać od jednego do czterech procesorów typu soft-core.

Wdrażany procesor soft-core to model VexRiscV oparty na architekturze listy rozkazów RISC-V. Procesor VexRiscV jest 32-bitową implementacją z rozszerzeniami dla przetwarzania potokowego i oferującą konfigurowalny zestaw funkcji, dzięki czemu doskonale nadaje się do stosowania w urządzeniach firmy Efinix. Opcjonalne konfiguracje obejmują powielacz, instrukcje atomowe, rozszerzenia zmiennoprzecinkowe i instrukcje skompresowane. W zależności od konfiguracji układu SoC, wydajność będzie się wahać w granicach od 0,86 do 1,05DMIPS/MHz.

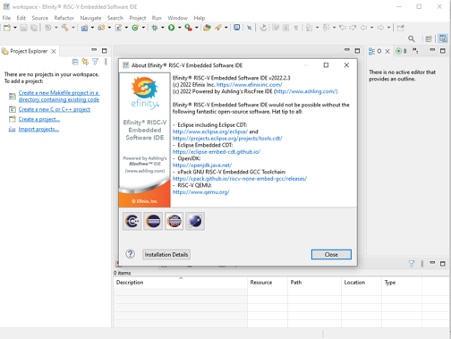

Po zaprojektowaniu i zaimplementowaniu środowiska sprzętowego w urządzeniu firmy Efinix, przy użyciu zintegrowanego środowiska deweloperskiego (IDE) Ashling RiscFree można opracować oprogramowanie aplikacyjne. Ashling RiscFree jest zintegrowanym środowiskiem deweloperskim (IDE) opartym na platformie Eclipse, umożliwiającym tworzenie i kompilację oprogramowania aplikacyjnego wraz z debugowaniem na urządzeniu docelowym w celu dopracowania aplikacji przed jej wdrożeniem.

Ilustracja 7: zintegrowane środowisko deweloperskie (IDE) Ashling RiscFree oparte na platformie Eclipse umożliwiające tworzenie i kompilację oprogramowania aplikacyjnego wraz z debugowaniem na urządzeniu docelowym. (Źródło ilustracji: Adam Taylor)

Ilustracja 7: zintegrowane środowisko deweloperskie (IDE) Ashling RiscFree oparte na platformie Eclipse umożliwiające tworzenie i kompilację oprogramowania aplikacyjnego wraz z debugowaniem na urządzeniu docelowym. (Źródło ilustracji: Adam Taylor)

W przypadku projektowania wbudowanych rozwiązań Linux za pomocą oprogramowania Buildroot dostarczane są wszystkie niezbędne artefakty rozruchowe, w tym First Stage Boot Loader, OpenSBI, U-Boot i Linux. Deweloper może również użyć systemu operacyjnego FreeRTOS, jeśli wymagane jest rozwiązanie czasu rzeczywistego.

Wdrażanie sztucznej inteligencji (AI)

Firma Efinix wdraża sztuczną inteligencję (AI), bazując na działaniu procesorów typu soft-core RISC-V. Wykorzystuje ona możliwości niestandardowych rozkazów procesora RISC-V, aby umożliwić przyspieszenia rozwiązań TensorFlow Lite. Wykorzystanie procesora RISC-V umożliwia użytkownikom również tworzenie niestandardowych instrukcji, które mogą być wykorzystywane w przetwarzaniu wstępnym lub końcowym następującym po wnioskowaniu z wykorzystaniem sztucznej inteligencji (AI), tworząc bardziej responsywne i deterministyczne rozwiązania.

Pierwszym krokiem w implementacji sztucznej inteligencji (AI) jest zapoznanie się z biblioteką modeli AI/ML Efinix zoptymalizowanych pod kątem technologii końcowej. Deweloperzy pracujący z urządzeniami firmy Efinix mają dostęp do zbioru modeli oraz sieci wytrenowanej przy użyciu platform Jupyter Notebooks lub Google Colab. Po wytrenowaniu sieci można ją przekonwertować z modelu zmiennoprzecinkowego na kwantyzowany za pomocą konwertera TensorFlow Lite.

Po uzyskaniu formatu TensorFlow Lite, do opracowania rozwiązania zgodnego z rozwiązaniem RISC-V można wykorzystać akcelerator tinyML firmy Efinix. Generator tinyML umożliwia deweloperom dostosowanie implementacji akceleratora i wygenerowanie plików projektu. Przy takim wdrożeniu przyspieszenie może wynosić od 4x do 200x w zależności od wybranej architektury i dostosowania.

Podsumowanie

Dzięki unikalnej architekturze XLR urządzenia firmy Efinix zapewniają deweloperom elastyczność. Narzędzia umożliwiają nie tylko realizację projektów RTL, ale także implementację złożonych rozwiązań SoC obejmujących procesory RISC-V typu soft-core. W oparciu o technologię SoC typu soft-core powstało rozwiązanie sztucznej inteligencji i uczenia maszynowego (AI/ML), które umożliwia wdrożenie wnioskowania ML.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.