Podstawy FPGA - część 4: pierwsze kroki z bezpośrednio programowalnymi macierzami bramek (FPGA) firmy Xilinx

Przekazane przez: Północnoamerykańscy redaktorzy DigiKey

2020-04-01

Uwaga od redakcji: optymalne rozwiązania w zakresie przetwarzania można zaprojektować łącząc RISC, CISC, procesory graficzne i macierze FPGA, same macierze FPGA lub macierze FPGA, które zawierają już procesory z rdzeniami twardymi w ramach swojej struktury. Wielu projektantów nie wie jednak, jakie są możliwości macierzy FPGA, jak się rozwinęły i jak z nich korzystać. W części 1 zawarto solidne wprowadzenie do macierzy FPGA, część 2 koncentruje się na ofercie macierzy FPGA firmy Lattice Semiconductor, natomiast część 3 skupia się na rodzinach urządzeń FPGA i narzędziach projektowych firmy Microchip Technology (od spółki zależnej Microsemi Corporation). W niniejszej części 4 omówiono komponenty i narzędzia firmy Xilinx. W części 5 przedstawiona zostanie oferta firmy Altera.

Jak wspomniano w części 1, bezpośrednio programowalne macierze bramek (FPGA) mają wiele cech, które sprawiają, że są one nieocenionymi zasobami obliczeniowymi, zarówno gdy działają same, jak i gdy są elementami niejednorodnej architektury. Wielu projektantów jednak nie zna macierzy FPGA i nie wie jak włączyć je do swoich projektów.

Jednym ze sposobów na pokonanie tej przeszkody jest głębsze przyjrzenie się architekturze FPGA i związanym z nią narzędziom oferowanym przez głównych producentów - ten artykuł poświęcony jest serii produktów firmy Xilinx.

Przegląd macierzy FPGA wysokiego poziomu

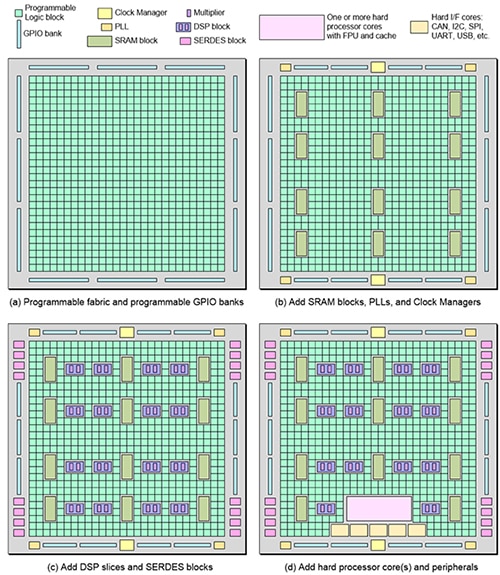

Na rynku istnieje wiele różnych typów macierzy FPGA, a każdy z nich charakteryzuje się inną funkcjonalnością i różnymi możliwościami kombinacji. Sercem każdej macierzy FPGA jest programowalna struktura. Jest ona zbudowana z szeregu programowalnych bloków logicznych, zwanych również elementami logicznymi (LE) (ilustracja 1a). Kolejnym etapem w projektowaniu struktury macierzy FPGA jest włączenie do niej elementów takich jak bloki pamięci SRAM, wewnętrzna pamięć blokowa RAM (BRAM), pętle synchronizacji fazy (PLL) oraz zarządzanie zegarem (ilustracja 1b). Można również dodać bloki cyfrowego przetwarzania sygnałów (zwanych DSP slice) oraz szybkie bloki SERDES (serializatory/deserializatory) (ilustracja 1c).

Ilustracja 1: najprostsza macierz FPGA zawiera tylko programowalną strukturę i wejścia-wyjścia ogólnego przeznaczenia, które można konfigurować (GPIO) (a), różne rodzaje architektury mogą wzmocnić podstawową strukturę blokami pamięci SRAM, pętlami PLL i zarządzaniem zegarami (b), blokami DSP i interfejsami SERDES (c), a także procesorami z rdzeniami twardymi i urządzeniami peryferyjnymi (d). (Źródło ilustracji: Max Maxfield)

Ilustracja 1: najprostsza macierz FPGA zawiera tylko programowalną strukturę i wejścia-wyjścia ogólnego przeznaczenia, które można konfigurować (GPIO) (a), różne rodzaje architektury mogą wzmocnić podstawową strukturę blokami pamięci SRAM, pętlami PLL i zarządzaniem zegarami (b), blokami DSP i interfejsami SERDES (c), a także procesorami z rdzeniami twardymi i urządzeniami peryferyjnymi (d). (Źródło ilustracji: Max Maxfield)

Funkcje interfejsów peryferyjnych takich jak CAN, I2C, SPI, UART i USB można zainstalować w strukturze w formie mikroprocesora z rdzeniem miękkim, ale wiele macierzy FPGA zawiera je już w płytce krzemowej w formie procesorów z rdzeniem twardym. Podobnie same mikroprocesory można zainstalować w strukturze w postaci rdzeni miękkich lub w postaci rdzeni twardych w płytce krzemowej (ilustracja 1d). Macierze FPGA z procesorami z rdzeniami twardymi są nazywane układami system-on-chip (SoC) FPGA. Różne macierze FPGA oferują różne zestawy funkcji, cech, możliwości i pojemności i są dostosowane do użytku na różnych rynkach i w różnych zastosowaniach.

Istnieje szereg sprzedawców macierzy FPGA, jak np. firma Altera (zakupiona przez Intel), Atmel (zakupiona przez Microchip Technology), Efinix, Lattice Semiconductor, Microsemi (również zakupiona przez Microchip Technology) oraz Xilinx.

Wszystkie te firmy oferują różne grupy macierzy FPGA - niektóre sprzedają macierze FPGA w systemie SoC, niektóre oferują urządzenia koncentrujące się na sztucznej inteligencji (AI) i uczeniu maszynowym (ML), a jeszcze inne oferują urządzenia odporne na promieniowanie, zaprojektowane z myślą o środowiskach o wysokim poziomie promieniowania, takich jak przestrzeń kosmiczna. Wybór najlepszego urządzenia do danego zadania może być trudny, ponieważ istnieje wiele grup produktów, a każda umożliwia korzystanie z innych zasobów.

Wprowadzenie do układów FPGA, SoC, MPSoC, RFSoC i ACAP firmy Xilinx

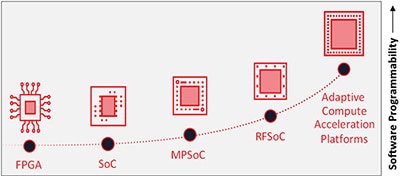

Parametry i możliwości programowalnych urządzeń w ofercie firmy Xilinx mieszczą się w zakresie od podstawowych do bardzo zaawansowanych. Oferta obejmuje tradycyjne macierze FPGA, SoC (programowalna macierz FPGA z procesorem z pojedynczym twardym rdzeniem), MPSoC (programowalna macierz FPGA z procesorami z wieloma rdzeniami twardymi), RFSoCs (MPSoC z funkcją RF) oraz platformy adaptacyjne ACAP (Adaptive Compute Acceleration Platforms) (ilustracja 2 ).

Ilustracja 2: z czasem portfolio architektur Xilinx ewoluowało od prostych macierzy FPGA zawierających tylko programowalną strukturę, przez urządzenia SoC, w których programowalna struktura jest uzupełniona o procesor sprzętowy, MPSoC z wieloma procesorami, RFSoC z funkcją RF, do najnowszej generacji platform ACAP, które są przeznaczone dla zastosowań w sztucznej inteligencji. (Źródło ilustracji: Max Maxfield)

Ilustracja 2: z czasem portfolio architektur Xilinx ewoluowało od prostych macierzy FPGA zawierających tylko programowalną strukturę, przez urządzenia SoC, w których programowalna struktura jest uzupełniona o procesor sprzętowy, MPSoC z wieloma procesorami, RFSoC z funkcją RF, do najnowszej generacji platform ACAP, które są przeznaczone dla zastosowań w sztucznej inteligencji. (Źródło ilustracji: Max Maxfield)

Xilinx ma tak szeroką ofertę produktów, obsługuje tak wiele segmentów rynku i zapewnia tak szeroki zakres metod wdrażania, że zrozumienie ich może być trudne dla kogoś, kto dopiero poznaje temat FPGA.

Jeśli chodzi o branże, w które celuje Xilinx, są to między innymi centra danych (obliczeniowe, sieciowe, magazynowe), komunikacja (przewodowa, bezprzewodowa), lotnictwo i obrona, przemysł, nauka i medycyna (ISM), testy, pomiary i emulacja (TME), oraz motoryzacja, nadawanie oraz rynek konsumencki.

Z kolei w wypadku metod wdrażania obejmują one to, co Xilinx nazywa sprzętowymi urządzeniami adaptacyjnymi (Hardware Adaptable Devices), które obejmują układy scalone, płytki ewaluacyjne i zestawy programistyczne, systemy końcowe obejmujące moduły SoM i karty akceleracyjne PCIe oraz FPGA w ramach usługi (FAAS), która obejmuje ocenę i wykorzystanie technologii Xilinx za pośrednictwem wiodących dostawców usług w chmurze, w tym Amazon Web Services (AWS), Alibaba.com i Nimbix.net

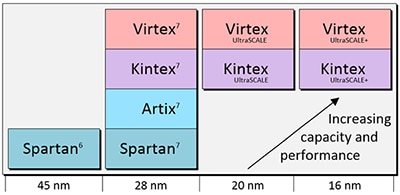

Jeśli chodzi o urządzenia Xilinx FPGA, można je skategoryzować według węzła technologii przetwarzania (ilustracja 3).

Ilustracja 3: oferta FPGA firmy Xilinx zapewnia kompleksowe urządzenia wielowęzłowe, aby sprostać wymaganiom w szerokim zakresie zastosowań. (Źródło ilustracji: Max Maxfield)

Ilustracja 3: oferta FPGA firmy Xilinx zapewnia kompleksowe urządzenia wielowęzłowe, aby sprostać wymaganiom w szerokim zakresie zastosowań. (Źródło ilustracji: Max Maxfield)

W zależności od docelowego zastosowania projektanci mogą zdecydować się na niskobudżetowy układ FPGA o małej powierzchni zaimplementowany na starszym węźle technologicznym lub, w przypadku najnowocześniejszych zastosowań sieciowych, wybrać na przykład wysokowydajne urządzenie o dużej przepustowości zaimplementowane w nowszym węźle technologicznym.

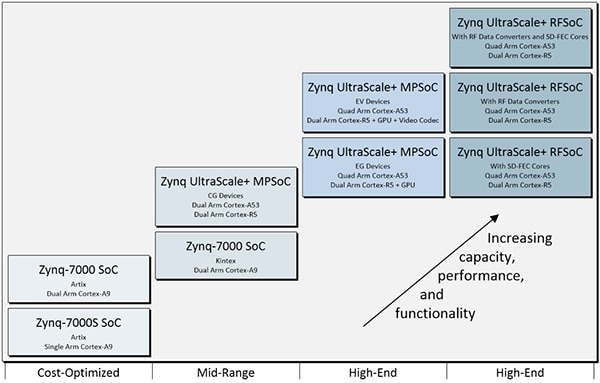

W przypadku projektów, które wymagają jednego lub większej liczby rdzeni twardych procesora (i innych funkcji sprzętowych, takich jak procesory graficzne, obsługa kodeków i rdzenie z korekcji błędów [SD-FEC]), Xilinx oferuje portfolio urządzeń pod wspólną nazwą Zynq. Podsumowanie ofert Zynq SoC, MPSoC i RFSoC przedstawiono na ilustracji 4. Ten zestaw rozwiązań zapewnia projektantom szeroki zakres możliwości ułatwiających optymalizację pod kątem mocy, wydajności, kosztów i czasu wprowadzenia na rynek.

Ilustracja 4: oferta SoC, MPSoC i RFSoC firmy Xilinx integruje programowalność procesora ze sprzętową programowalnością macierzy FPGA, zapewniając projektantom wydajność, elastyczność i skalowalność systemu. (Źródło ilustracji: Max Maxfield)

Ilustracja 4: oferta SoC, MPSoC i RFSoC firmy Xilinx integruje programowalność procesora ze sprzętową programowalnością macierzy FPGA, zapewniając projektantom wydajność, elastyczność i skalowalność systemu. (Źródło ilustracji: Max Maxfield)

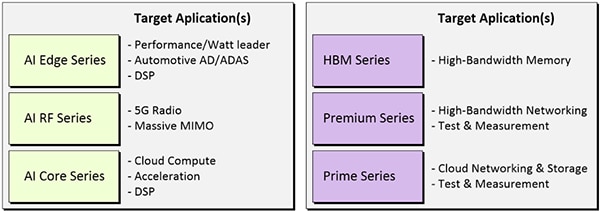

Najnowsze dziecko oferty firmy Xilinx to urządzenia Versal Adaptive Compute Acceleration Platform (ACAP), wszystkie zaimplementowane w węźle technologicznym 7 nanometrów (nm). ACAP to wysoce zintegrowane, wielordzeniowe platformy obliczeniowe, które mogą dostosować się do ewoluujących i różnorodnych algorytmów. Można je dynamicznie dostosowywać na poziomie sprzętu i oprogramowania, aby pasowały do szerokiej gamy zastosowań i obciążeń. Zbudowane wokół programowalnej sieci NoC (Network on Chip), platformy ACAP są łatwe do programowania zarówno przez projektantów sprzętu, jak i programistów.

Nowe funkcje w urządzeniach Versal obejmują inteligentne silniki (szeroka gama procesorów wektorowych dla ML i DSP), programowalne sieci NoC o wysokiej przepustowości, niskim opóźnieniu i niskim poborze mocy, które zdolne są przesyłać terabajty danych oraz zintegrowaną strukturę zapewniającą lepszą wydajność, użyteczność i produktywność dzięki wstępnie zbudowanej infrastrukturze podstawowej i łączności systemowej.

Przegląd oferty Versal ACAP przedstawiono na ilustracji 5.

Ilustracja 5: Versal ACAP firmy Xilinx to wysoce zintegrowane, wielordzeniowe platformy obliczeniowe, które mogą dostosować się do ewoluujących i różnorodnych algorytmów. Urządzenia ACAP można dynamicznie dostosowywać na poziomie sprzętu i oprogramowania, aby pasowały do szerokiej gamy zastosowań i obciążeń. (Źródło ilustracji: Max Maxfield)

Ilustracja 5: Versal ACAP firmy Xilinx to wysoce zintegrowane, wielordzeniowe platformy obliczeniowe, które mogą dostosować się do ewoluujących i różnorodnych algorytmów. Urządzenia ACAP można dynamicznie dostosowywać na poziomie sprzętu i oprogramowania, aby pasowały do szerokiej gamy zastosowań i obciążeń. (Źródło ilustracji: Max Maxfield)

Jak zostanie to omówione w części dotyczącej narzędzi projektowych, kluczowym wyróżnikiem związanym z urządzeniami Versal jest nowy zestaw oprogramowania, skierowany do analityków danych i inżynierów oprogramowania, a także do inżynierów projektowania tradycyjnego sprzętu.

Obecnie dostępna jest cała gama urządzeń firmy Xilinx. Kilka reprezentatywnych przykładów oferty to Artix-7 FPGA, Kintex UltraScale FPGA, Kintex UltraScale+ FPGA, moduł Zynq-7000 SoC firmy Trenz Electronic GmbH oraz Zynq UltraScale+ MPSoC.

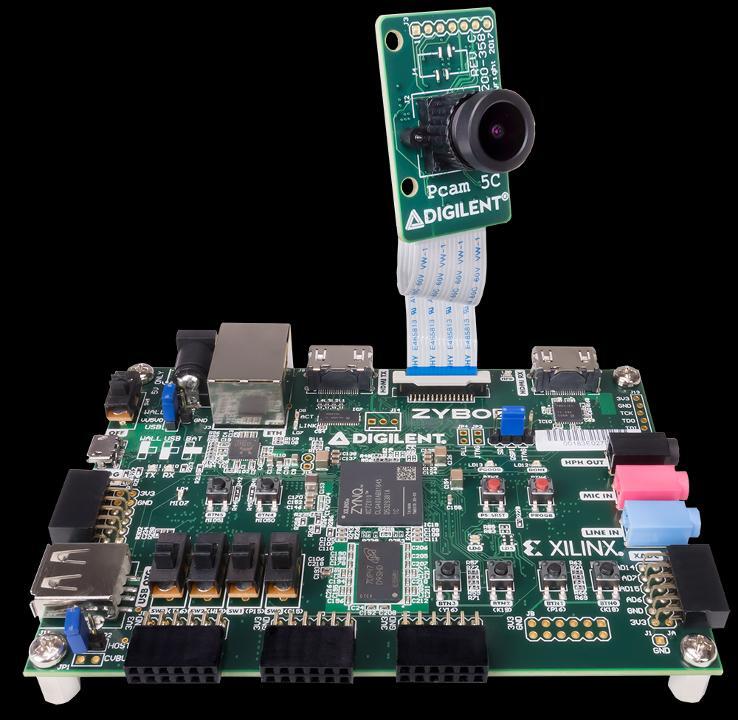

Podobnie szeroki jest wybór płytek ewaluacyjnych i rozwojowych. Oto kilka przykładów z oferty: płytka ewaluacyjna Artix-7 FPGA firmy Digilent, płytka ewaluacyjna Kintex UltraScale FPGA firmy Analog Devices, płytka ewaluacyjna Kintex UltraScale+ FPGA firmy Xilinx, płytka ewaluacyjna Zynq-7000 SoC FPGA firmy Digilent oraz płytka ewaluacyjna Zynq UltraScale+ MPSoC FPGA, również firmy Xilinx.

Projektowanie i prace rozwojowe przy użyciu urządzeń FPGA, SoC i ACAP firmy Xilinx

Jednym z obszarów, w którym Xilinx naprawdę wyróżnia się na tle konkurencji, jest szeroka gama narzędzi do projektowania i przepływów.

W części 1 serii o macierzach FPGA wspomniano, że inżynierowie tradycyjnie projektują takie urządzenia przy użyciu języka opisu sprzętu (hardware description language, HDL), takiego jak Verilog lub VHDL do określenia celu projektu na poziomie abstrakcji (tzw. register transfer level, RTL). Opisy RTL mogą być najpierw symulowane w celu sprawdzenia, czy działają zgodnie z wymaganiami, a następnie są przekazywane do narzędzia do syntezy, które generuje plik konfiguracyjny używany do programowania macierzy FPGA.

Następnym krokiem jest uchwycenie zamiaru projektu za pomocą języka programowania, takiego jak C/C++, lub specjalnej implementacji, takiej jak SystemC, która jest zestawem klas C++ i makr, które zapewniają interfejs symulacji sterowany zdarzeniami. Ułatwiają one symulację współbieżnych procesów, z których każdy opisany jest z użyciem prostej składni C++. Takie opisy można analizować i profilować, uruchamiając jak zwykłe programy, po czym są one przekazywane do silnika syntezy wysokiego poziomu (HLS), który wysyła RTL do standardowego kompilatora syntezy.

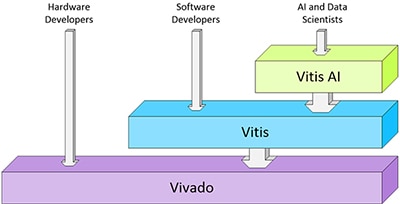

Wszystkie te funkcje realizuje pakiet Vivado Design Suite HLx Editions, który generuje strumień bitów konfiguracji ładowany do docelowych urządzeń FPGA, SoC, MPSoC, RFSoC lub ACAP. Oprócz umożliwienia twórcom sprzętu wykorzystania projektu opartego na języku C i zoptymalizowanego ponownego wykorzystania, Vivado zapewnia również ponowne wykorzystanie podsystemu własności intelektualnej (IP), automatyzację integracji i przyspieszone zamknięcie projektu (ilustracja 6).

Ilustracja 6: przegląd wysokiego poziomu zestawu narzędzi do projektowania Vivado i Vitis firmy Xilinx pokazuje, w jaki sposób użytkownicy mogą pracować z narzędziami na najbardziej odpowiednich poziomach abstrakcji. Projektanci sprzętu pracują na Vivado, twórcy oprogramowania pracują na Vitis, a naukowcy pracujący nad sztuczną inteligencją i analitycy danych na Vitis AI. (Źródło ilustracji: Max Maxfield)

Ilustracja 6: przegląd wysokiego poziomu zestawu narzędzi do projektowania Vivado i Vitis firmy Xilinx pokazuje, w jaki sposób użytkownicy mogą pracować z narzędziami na najbardziej odpowiednich poziomach abstrakcji. Projektanci sprzętu pracują na Vivado, twórcy oprogramowania pracują na Vitis, a naukowcy pracujący nad sztuczną inteligencją i analitycy danych na Vitis AI. (Źródło ilustracji: Max Maxfield)

Vitis Unified Software Platform obsługuje następny poziom abstrakcji, który zapewnia twórcom oprogramowania możliwość płynnego tworzenia przyspieszonych aplikacji. Można powiedzieć, że Vitis AI znajduje się na szczycie Vitis, umożliwiając naukowcom pracującym ze sztuczną inteligencją i analitykom danych pracę na poziomie abstrakcji TensorFlow. Vitis AI to platforma programistyczna do wnioskowania z wykorzystaniem sztucznej inteligencji (AI) na platformach sprzętowych firmy Xilinx, w tym na urządzeniach brzegowych, jak i kartach Alveo PCIe. Składa się ze zoptymalizowanej własności intelektualnej (IP), narzędzi, bibliotek, modeli i przykładowych projektów, a jej celem jest wykorzystanie pełnego potencjału akceleracji AI na urządzeniach FPGA i ACAP firmy Xilinx.

Vitis AI przesyła dane do oprogramowania Vitis, które przesyła dane do Vivado. Kluczową kwestią widoczną na ilustracji 6 jest to, że użytkownicy „widzą” tylko to, co potrzebują „widzieć”. Oznacza to, że twórcy sprzętu „zobaczą” tylko Vivado, twórcy oprogramowania „zobaczą” Vitis, a naukowcy pracujący ze sztuczną inteligencją i analitycy danych „zobaczą” Vitis AI. W ten sposób użytkownicy mogą pracować z narzędziami na najbardziej odpowiednich poziomach abstrakcji.

Dzięki dostarczeniu programistom takiego pakietu narzędzi jak Vitis, który izoluje ich od bazowego sprzętu, macierze FPGA stają się dostępniejsze dla znacznie większej puli programistów. Podobnie, dostarczanie naukowcom pracującym z AI i analitykom danych pakietu narzędzi, takiego jak Vitis AI, pozwalającego im skupić się na własnym poziomie abstrakcji i izolującego ich od bazowego oprogramowania, również otwiera świat FPGA dla nowej grupy programistów.

Zapewniając te możliwości, firma Xilinx jest liderem w branży w dziedzinie starań przenoszenia narzędzi FPGA na coraz wyższe poziomy abstrakcji projektowej, co pozwoli konstruktorom łatwiej wykorzystać możliwości tych urządzeń i integrować je w kolejnych projektach.

Podsumowanie

Optymalne rozwiązania w zakresie projektowania przetwarzania można stworzyć łącząc procesory i macierze FPGA, same macierze FPGA lub macierze FPGA, które zawierają już procesory z rdzeniami twardymi w swojej strukturze. Jako technologia, macierze FPGA rozwijały się szybko na przestrzeni lat i dzięki elastyczności, szybkości przetwarzania i mocy są w stanie sprostać wielu wymaganiom projektowym, co sprawia, że są idealnym wyborem w wielu zastosowaniach - od inteligentnych interfejsów po systemy wizyjne i sztuczną inteligencję.

Jak pokazano, oferta programowalnych urządzeń firmy Xilinx obejmuje urządzenia od podstawowych do bardzo zaawansowanych pod względem wydajności i możliwości. Należą do nich tradycyjne macierze FPGA, SoC (programowalna macierz FPGA z procesorem z jednym rdzeniem twardym), MPSoC (programowalna macierz FPGA z procesorami z wieloma rdzeniami sprzętowymi), RFSoCs (MPSoC z funkcją RF) oraz platformy adaptacyjne ACAP (Adaptive Compute Acceleration Platforms).

Aby pomóc projektantom w tworzeniu projektów za pomocą tych urządzeń, firma Xilinx oferuje pakiet narzędzi spełniających potrzeby programistów sprzętu (Vivado), programistów (Vitis) oraz specjalistów od sztucznej inteligencji i analityków danych (Vitis AI).

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.