Wykorzystanie sprawnego nadajniko-odbiornika na częstotliwości radiowe (RF) w adaptacyjnym systemie łączności w technologii radia programowalnego (SDR) w lotnictwie i kosmonautyce oraz obronności

Przekazane przez: Północnoamerykańscy redaktorzy DigiKey

2023-11-30

Projektanci systemów dla lotnictwa i kosmonautyki oraz obronności (ADEF) stoją w obliczu niesłabnącego zapotrzebowania na systemy komunikacyjne o niższej mocy i bardziej kompaktowych rozmiarach, które są w stanie sprawnie reagować na dynamiczne środowisko sygnałów. Wykraczając poza tradycyjną architekturę radiową, technologia radia programowalnego (SDR) może pomóc w spełnieniu szybko zmieniających się wymagań dla radioodbiorników ADEF, jednak jej wdrożenie wiąże się z wieloma wyzwaniami w zakresie spełnienia wymagań funkcjonalnych, a także potrzeby zmniejszenia rozmiarów, wagi i mocy (SWaP).

W niniejszym artykule opisano skuteczniejsze rozwiązanie w technologii radia programowalnego (SDR) firmy Analog Devices, które pozwala uprościć projektowanie kompaktowych i elastycznych systemów komunikacyjnych o niskiej mocy bez pogorszenia parametrów działania.

Pojawiające się wyzwania stawiają coraz wyższe wymagania

Projektanci stoją w obliczu zapotrzebowania na bardziej efektywną komunikację w coraz większej liczbie zastosowań przemysłowych i zastosowań o znaczeniu krytycznym, między innymi w bezpiecznej komunikacji radiowej, radarach adaptacyjnych, środkach walki elektronicznej i ulepszonej nawigacji GPS. Te nowe wyzwania dyktują potrzebę ulepszonego działania szerokopasmowego, wyższego zakresu dynamiki, większej zdolność do wyboru częstotliwości oraz większej możliwości rekonfiguracji. Jednak wyższe wymagania funkcjonalne mogą kolidować z potrzebą mniejszych rozmiarów, wagi i mocy (SWaP), ponieważ systemy komunikacyjne przechodzą na mniejsze platformy zasilane bateryjnie, na przykład w bezzałogowych statkach powietrznych (UAS) i urządzeniach przenośnych.

Rozwiązania projektowe oparte na tradycyjnych dyskretnych superheterodynowych architekturach radiowych oferują wysokie parametry działania, szeroki zakres dynamiki i minimalny poziom szumów. Dla projektantów wyzwanie polegające na odizolowaniu pożądanego sygnału od częstotliwości pośredniej (IF), będącej istotą tego podejścia, zwykle skutkuje skomplikowanymi projektami o dużych rozmiarach, wadze i mocy (SWaP) i niewielkiej lub zerowej możliwości rekonfiguracji (ilustracja 1).

Ilustracja 1: tradycyjne superheterodynowe architektury radiowe mogą spełniać docelowe parametry działania, ale ich złożoność uniemożliwia osiągnięcie nowych celów w dziedzinie minimalnych rozmiarów, wagi i mocy (SWaP). (Źródło ilustracji: Analog Devices)

Ilustracja 1: tradycyjne superheterodynowe architektury radiowe mogą spełniać docelowe parametry działania, ale ich złożoność uniemożliwia osiągnięcie nowych celów w dziedzinie minimalnych rozmiarów, wagi i mocy (SWaP). (Źródło ilustracji: Analog Devices)

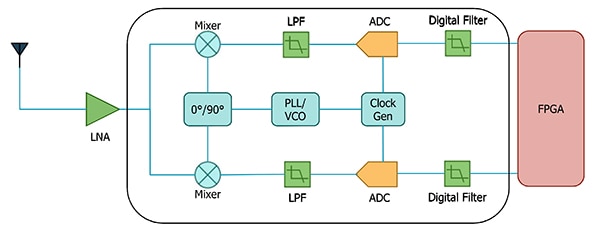

Z kolei architektury z konwersją bezpośrednią (zerowe częstotliwości pośrednie (IF)) zmniejszają zarówno wymagania dotyczące filtrowania, jak i potrzebę stosowania przetworników analogowo-cyfrowych (ADC) o bardzo dużej szerokości pasma, co skutkuje prostszą konstrukcją, którą można zaimplementować na jednym układzie półprzewodnikowym (ilustracja 2).

Ilustracja 2: architektury radiowe o zerowych częstotliwościach pośrednich (IF) mogą zaspokoić zapotrzebowanie na wyższe parametry i niższe rozmiary, wagi i moce (SWaP), jednak wyzwanie stanowi tutaj izolacja sygnału. (Źródło ilustracji: Analog Devices)

Ilustracja 2: architektury radiowe o zerowych częstotliwościach pośrednich (IF) mogą zaspokoić zapotrzebowanie na wyższe parametry i niższe rozmiary, wagi i moce (SWaP), jednak wyzwanie stanowi tutaj izolacja sygnału. (Źródło ilustracji: Analog Devices)

Pomimo oczywistych zalet, architektura o konwersji bezpośredniej wiąże się z własnymi wyzwaniami wdrożeniowymi, które ograniczyły jej szerokie zastosowanie. W tej architekturze sygnał jest konwertowany na nośną o częstotliwości radiowej (RF) na częstotliwości oscylatora lokalnego (LO), ale błędy niezrównoważenia prądu stałego i upływ oscylatora lokalnego mogą powodować propagację błędów w łańcuchu sygnałowym. Co więcej, różnice w ścieżkach sygnałowych, nawet w obrębie tego samego układu półprzewodnikowego, mogą wprowadzać niedopasowanie wzmocnienia lub fazy sygnałów fazowych (I) i kwadraturowych (Q), co skutkuje błędem kwadraturowym, który może pogarszać izolowanie sygnału.

Technologia radia programowalnego (SDR) pozwala przezwyciężyć ograniczenia tradycyjnych architektur radiowych, ale niewiele rozwiązań jest w stanie sprostać szerszym wymaganiom związanym z zastosowaniami w lotnictwie i kosmonautyce oraz obronności (ADEF). Używając nadajniko-odbiornika ADRV9002 firmy Analog Devices, deweloperzy mogą z łatwością zaspokoić potrzebę poprawy parametrów działania i zwiększenia funkcjonalności przy niższych rozmiarach, wagach i mocy (SWaP) wymaganych we wspomnianych zastosowaniach.

Zintegrowane funkcje zapewniają zoptymalizowane parametry działania przy zmniejszonych rozmiarach, wadze i mocy (SWaP)

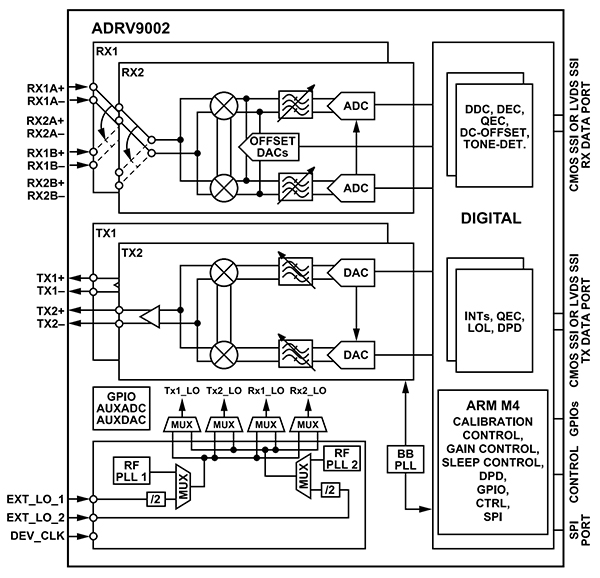

Wysokozintegrowany nadajniko-odbiornik ADRV9002 obsługuje zakres częstotliwości od 30MHz do 6000MHz i zawiera wszystkie radiowe funkcje sygnałów mieszanych oraz cyfrowych niezbędne do obsługi szerokiego zakresu wymagań zastosowań. Urządzenie może pracować zarówno w trybie dupleksowym z podziałem czasu (TDD), jak i w trybie dupleksowym z podziałem częstotliwości (FDD). Urządzenie posiada oddzielne podsystemy odbiornika i nadajnika z dwukanałową konwersją bezpośrednią, które zawierają programowane filtry cyfrowe, korekcję niezrównoważenia prądu stałego oraz korekcję błędu kwadraturowego (QEC).

W obrębie podsystemu syntezatora na układzie półprzewodnikowym, urządzenie ADRV9002 posiada dwa odrębne tory pętli synchronizacji fazowej (PLL): jedną dla toru wysokiej częstotliwości RF, a drugą dla zegarów cyfrowych i zegarów próbkujących przetworników. Wreszcie blok cyfrowego przetwarzania sygnału urządzenia zawiera wbudowany procesor M4 Arm®, który obsługuje funkcje autokalibracji i sterowania (ilustracja 3).

Ilustracja 3: nadajniko-odbiornik częstotliwości radiowych (RF) ADRV9002 zawiera dwa podsystemy: odbiorczy (RX) i nadawczy (TX). (Źródło ilustracji: Analog Devices)

Ilustracja 3: nadajniko-odbiornik częstotliwości radiowych (RF) ADRV9002 zawiera dwa podsystemy: odbiorczy (RX) i nadawczy (TX). (Źródło ilustracji: Analog Devices)

Urządzenie ADRV9002 może działać w trybie zerowych lub niskich częstotliwości pośrednich (IF) w zastosowaniach wrażliwych na zakłócenia fazowe. Zawiera podsystemy nadawczy i odbiorczy stanowiące kompletne łańcuchy sygnałowe. Każdy podsystem nadajnika zawiera parę przetworników cyfrowo-analogowych (DAC), filtrów i mikserów, które dokonują rekombinacji sygnałów I i Q oraz ich modulacji na częstotliwości nośnej w celu transmisji.

Każdy podsystem odbiornika zawiera rezystancyjną sieć wejściową do sterowania wzmocnieniem, która zasila pasywny mikser działający w trybie prądowym. Z kolei wzmacniacz transimpedancyjny konwertuje prąd wyjściowy miksera na poziom napięcia, który jest przetwarzany na postać cyfrową przez przetwornik analogowo-cyfrowy o wysokim zakresie dynamiki. W czasie luk pracy nadajnika w trybie dupleksowym z podziałem czasu (TDD) lub dupleksowym z podziałem częstotliwości (FDD), w których używany jest tylko jeden system odbiornika, nieużywane wejścia odbiornika mogą być wykorzystywane do monitorowania kanałów nadajnika pod kątem upływu oscylatora lokalnego i korekcji błędu kwadraturowego lub do monitorowania poziomów sygnału wyjściowego wzmacniacza mocy (PA).

Ta ostatnia funkcja pojawia się w zintegrowanej funkcji cyfrowej korekcji wstępnych zniekształceń (DPD) urządzenia ADRV9002, która wykorzystuje monitorowane poziomy sygnału wzmacniacza mocy (PA) do zastosowania odpowiedniej korekcji zniekształceń wstępnych wymaganej do linearyzacji sygnału wyjściowego. Dzięki temu urządzenie ADRV9002 może sterować wzmacniaczem mocy (PA) bliżej poziomu nasycenia, optymalizując jego sprawność.

Strojenie mocy i parametrów działania

Urządzenie ADRV9002 stanowi w pełni zintegrowane rozwiązanie w obudowie CSP ze 196 wyprowadzeniami sferycznymi w siatce rastrowej (BGA). Minimalizuje ono rozmiary bazujących na radiu programowalnym (SDR) systemów komunikacyjnych do zastosowań w lotnictwie i kosmonautyce oraz obronności (ADEF). Aby pomóc deweloperom w dalszej optymalizacji poboru mocy, układ ADRV9002 wyposażono w wiele funkcji zaprojektowanych specjalnie, aby pomóc deweloperom w znalezieniu odpowiedniej równowagi między dobrymi parametrami działania a mocą.

Na poziomie poszczególnych bloków ścieżki sygnałowej deweloperzy mogą wdrożyć skalowanie mocy, w celu obniżenia poboru mocy kosztem ograniczenia parametrów działania. Ponadto bloki w ramkach odbioru (RX) i nadawania (TX) w trybie dupleksowym z podziałem czasu (TDD) można wyłączyć, aby obniżyć pobór mocy, poświęcając krótszy czas realizacji komunikacji w kierunku odbiór-nadawanie (RX/TX) i nadawanie-odbiór (TX/RX). Aby jeszcze bardziej ułatwić deweloperom optymalizację poboru mocy w stosunku do parametrów działania, w każdym podsystemie odbiornika ADRV9002 przewidziano dwie pary przetworników analogowo-cyfrowych (ADC). Jedna para zawiera wysokowydajne przetworniki analogowo-cyfrowe (ADC) typu sigma-delta, natomiast druga para może stanowić alternatywę na wypadek scenariusza, w którym pobór mocy ma znaczenie krytyczne.

W przypadku zastosowań charakteryzujących się okresami bezczynności można wykorzystać tryb monitorowania odbioru (RX) urządzenia ADRV9002. W tym trybie urządzenie ADRV9002 przełącza się pomiędzy stanem uśpienia z minimalnym poborem mocy i stanem wykrywania w zaprogramowanym cyklu roboczym. W stanie wykrywania urządzenie aktywuje odbiornik i próbuje odebrać sygnał w zaprogramowanym przez dewelopera paśmie częstotliwości i w częstotliwości oscylatora lokalnego odbioru (RX). Jeśli zmierzony przez urządzenie poziom mocy sygnału przewyższa zaprogramowaną wartość progową, urządzenie wychodzi z trybu monitorowania, a bloki urządzenia ADRV9002 są zasilane w celu obsługi żądanego sygnału.

Szybkie prototypowanie i prace rozwojowe

Aby pomóc inżynierom w szybkim przejściu do ewaluacji, prototypowania i prac rozwojowych, firma Analog Devices zapewnia szerokie wsparcie sprzętowe i programowe dla systemów opartych na urządzeniu ADRV9002.

Jeśli chodzi o wsparcie sprzętowe, firma Analog Devices oferuje dwie karty oparte na urządzeniu ADRV9002:

- ADRV9002NP/W1/PCBZ do zastosowań w dolnych pasmach w zakresie od 30MHz do 3GHz

- ADRV9002NP/W2/PCBZ do zastosowań w górnych pasmach w zakresie od 3 do 6GHz

Wyposażone w złącza FMC, karty te obsługują wbudowane układy ADRV9002 z regulacją mocy i interfejsami sprzętowymi, a także dystrybucją synchronizacji zegara z wieloma układami (MCS). Omawiane karty podłącza się za pośrednictwem złącza FMC do płyty głównej z bezpośrednio programowalną macierzą bramek (FPGA), np. płytką ewaluacyjną ZCU102 firmy AMD do sterowania zasilaniem i aplikacjami.

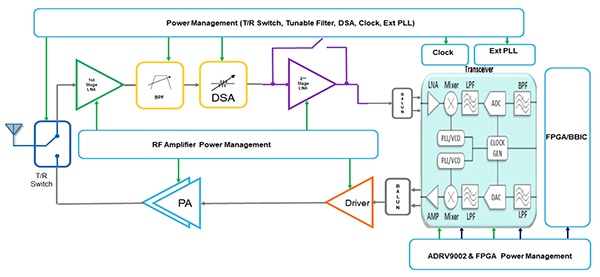

Firma Analog Devices dostarcza w pakiecie wsparcia kompletny schemat i wykaz materiałów (BOM) dla swoich kart radiowych ADRV9002NP. Schemat i wykaz materiałów (BOM) stanowią skuteczny punkt wyjścia do opracowywania niestandardowych urządzeń dla większości zastosowań. Niektóre zastosowania wymagają dodatkowego układu front-end na częstotliwości radiowe (RF), aby spełnić określone wymagania dotyczące kondycjonowania sygnału. W przypadku takich zastosowań deweloperzy potrzebują tylko kilku dodatkowych komponentów, aby dokończyć projekt (ilustracja 4).

Ilustracja 4: wysoce zintegrowany nadajniko-odbiornik ADRV9002 umożliwia deweloperom szybkie wdrażanie specjalistycznych projektów. (Źródło ilustracji: Analog Devices)

Ilustracja 4: wysoce zintegrowany nadajniko-odbiornik ADRV9002 umożliwia deweloperom szybkie wdrażanie specjalistycznych projektów. (Źródło ilustracji: Analog Devices)

W tym przykładzie deweloperzy mogą szybko wdrożyć odpowiedni układ front-end na częstotliwości radiowe (RF) przy użyciu następujących komponentów zarządzania zasilaniem firmy Analog Devices:

- Przełącznik na częstotliwości radiowe (RF) ADRF5160

- Wzmacniacz niskoszumowy (LNA) HMC8411

- Cyfrowo strojony filtr pasmowo-przepustowy ADMV8526

- Cyfrowy tłumik krokowy (DSA) HMC1119 na częstotliwości radiowe

- Wzmacniacz sterownika HMC8413

- Wzmacniacz mocy (PA) HMC8205B

Firma Analog Devices zapewnia kompleksowe wsparcie w zakresie tworzenia oprogramowania w postaci dokumentacji i pakietów oprogramowania do pobrania. Deweloperzy korzystający ze wspomnianego powyżej sprzętu rozwojowego mogą kontynuować prototypowanie i prace rozwojowe w oparciu o linię produktów oprogramowania firmy Analog Devices lub pakiety oprogramowania otwartoźródłowego.

Zakres niniejszego artykułu ogranicza się do omówienia oprogramowania wspomnianej linii produktów. Więcej informacji na temat metodologii rozwoju z wykorzystaniem narzędzi otwartoźródłowych zawiera podręcznik użytkownika platformy prototypowej ADRV9001/2 firmy Analog Devices.Firma Analog Devices zastrzega, że oznaczenie „ADRV9001” w dokumentacji pomocniczej firmy należy rozumieć jako oznaczenie grupy obejmującej zarówno urządzenie ADRV9002 jak i inne produkty z grupy ADRV9001. W związku z tym odwołania do urządzeń ADRV9001 we wspomnianym tekście lub na ilustracjach odnoszą się także do urządzenia ADRV9002 będącego przedmiotem niniejszego artykułu.

W zestawie rozwojowym oprogramowania (SDK) linii produktów firmy Analog Devices dostępne jest oparte na systemie Windows narzędzie programowe do ewaluacji nadajniko-odbiorników (TES) stanowiące przystępny punkt wyjścia do szybkiej konfiguracji i ewaluacji parametrów działania nadajniko-odbiornika.

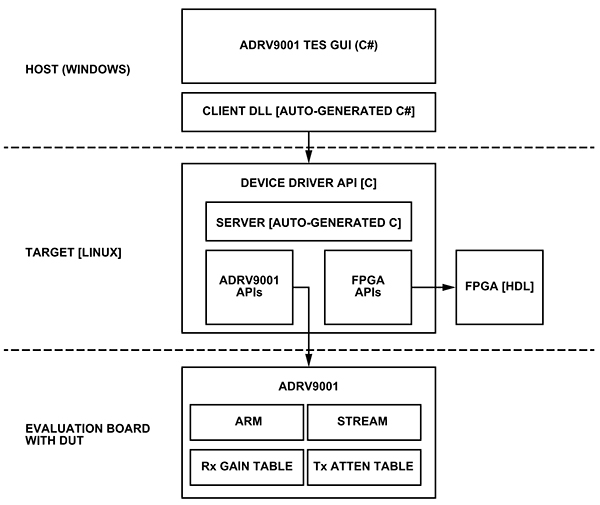

Na potrzeby ewaluacji i prototypowania z użyciem kart ADRV9002 firmy Analog Devices i płytki ewaluacyjnej ZCU102 firmy AMD narzędzie TES udostępnia graficzny interfejs użytkownika (GUI) do konfigurowania sprzętu i obserwacji przechwyconych danych (ilustracja 5).

Ilustracja 5: dostępne w zestawie rozwojowym oprogramowania (SDK) narzędzie programowe do ewaluacji nadajniko-odbiorników (TES) pozwala deweloperom na szybkie rozpoczęcie ewaluacji nadajniko-odbiornika ADRV9002 na obsługiwanej platformie ewaluacyjnej. (Źródło ilustracji: Analog Devices)

Ilustracja 5: dostępne w zestawie rozwojowym oprogramowania (SDK) narzędzie programowe do ewaluacji nadajniko-odbiorników (TES) pozwala deweloperom na szybkie rozpoczęcie ewaluacji nadajniko-odbiornika ADRV9002 na obsługiwanej platformie ewaluacyjnej. (Źródło ilustracji: Analog Devices)

Narzędzie TES automatycznie generuje kod w języku C#, który można skompilować do środowiska Linux, MATLAB lub języka Python. Zestaw rozwojowy oprogramowania (SDK) zawiera pełny zestaw bibliotek oprogramowania i interfejsów programowania aplikacji (API), w tym pakiet API ADRV9001 opracowany dla platformy AMD ZCU102.

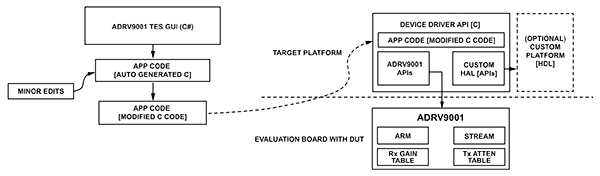

Tok prac zestawu rozwojowego oprogramowania (SDK) umożliwia również bezpośrednio migrację ze środowiska ewaluacji i prototypowania z płytką ewaluacyjną do niestandardowego środowiska docelowego dewelopera (ilustracja 6).

Ilustracja 6: architektura zestawu rozwojowego oprogramowania (SDK) pozwala deweloperom na łatwe przeniesienie wyników ewaluacji na własną platformę docelową. (Źródło ilustracji: Analog Devices)

Ilustracja 6: architektura zestawu rozwojowego oprogramowania (SDK) pozwala deweloperom na łatwe przeniesienie wyników ewaluacji na własną platformę docelową. (Źródło ilustracji: Analog Devices)

W tym toku migracji deweloper pozwala narzędziu TES na automatyczne wygenerowanie kodu, jak poprzednio. Jednak zamiast używać go bezpośrednio, deweloper wdraża edytowaną wersję wygenerowanego kodu na platformie docelowej. W praktyce wymagane edycje ograniczają się głównie do usunięcia wywołań funkcji, które odnoszą się do komponentów sprzętowych rozpoznawanych przez narzędzie TES, ale niepotrzebnych w systemie docelowym. Architektura zestawu rozwojowego oprogramowania (SDK) zawiera interfejs warstwy abstrakcji sprzętowej (HAL) pomiędzy biblioteką ADRV9001 a sprzętem dewelopera, więc deweloperzy muszą tylko dostarczyć niestandardowy kod, który implementuje kod interfejsu warstwy abstrakcji sprzętowej (HAL) dla konkretnego sprzętu. W rezultacie deweloperzy mogą szybko przejść od ewaluacji z użyciem kart firmy Analog Devices i płytki AMD do prac rozwojowych pod kątem własnego niestandardowego środowiska docelowego.

Podsumowanie

Zastosowania w lotnictwie i kosmonautyce oraz obronności (ADEF) stają przed coraz większymi wyzwaniami w coraz bardziej złożonym środowisku sygnałowym. Wraz z zaspokojeniem zapotrzebowania na wyższe parametry działania w szerszym zakresie częstotliwości, deweloperzy muszą zmniejszać rozmiary, wagi i moce (SWaP), aby usprawnić migrację w zastosowaniach do systemów z zasilaniem bateryjnym. Korzystając z wysoce zintegrowanego nadajniko-odbiornika firmy Analog Devices, deweloperzy mogą wdrażać rozwiązania w technologii radia programowalnego (SDR), aby skuteczniej sprostać wspomnianym wymaganiom.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.