Przeznaczenie i sposób używania bezpośrednio programowalnych macierzy bramek (FPGA) firmy Efinix do obrazowania AI/ML – część 2: przechwytywanie i przetwarzanie obrazów

Przekazane przez: DigiKey's European Editors

2023-05-05

Uwaga od redakcji: nowe podejścia do architektur bezpośrednio programowalnych macierzy bramek (FPGA) zwiększają kontrolę i elastyczność, pozwalając na sprostanie potrzebom uczenia maszynowego (ML) i sztucznej inteligencji (AI). Część 1 tej dwuczęściowej serii przedstawia przykład takiej architektury firmy Efinix oraz sposób rozpoczęcia z nią pracy przy użyciu płytki rozwojowej. W części 2 omówiono podłączanie płytki rozwojowej do urządzeń zewnętrznych i peryferyjnych, takich jak kamera, a także sposób wykorzystania układu bezpośrednio programowalnej macierzy bramek (FPGA) w celu usunięcia wąskich gardeł przetwarzania obrazu.

Macierze FPGA odgrywają kluczową rolę w wielu zastosowaniach, od kontroli przemysłowej i bezpieczeństwa po robotykę, lotnictwo i motoryzację. Dzięki elastycznej charakterystyce programowalnego rdzenia logicznego i jego szerokim możliwościom współpracy, jednym z rozwijających się zastosowań macierzy FPGA jest przetwarzanie obrazu, w którym można zastosować uczenie maszynowe (ML). Dzięki równoległej strukturze logicznej bezpośrednio programowalne macierze bramek (FPGA) doskonale sprawdzają się we wdrażaniu rozwiązań zawierających kilka szybkich interfejsów kamer. Ponadto macierze FPGA umożliwiają użycie dedykowanych potoków przetwarzania w układach logicznych, eliminując w ten sposób wąskie gardła współużytkowania zasobów związane z rozwiązaniami opartymi na procesorach lub procesorach graficznych (GPU).

Drugie spojrzenie na bezpośrednio programowalne macierze bramek (FPGA) Titanium firmy Efinix przedstawia przykładowe zastosowanie do przetwarzania obrazu, które jest dostarczane z płytką rozwojową FPGA Ti180 M484. Celem jest zrozumienie części składowych projektu i określenie, gdzie technologia bezpośrednio programowalnych macierzy bramek (FPGA) umożliwia usunięcie zatorów lub zapewnia deweloperom inne korzyści.

Projekt referencyjny oparty na urządzeniu Ti180 M484

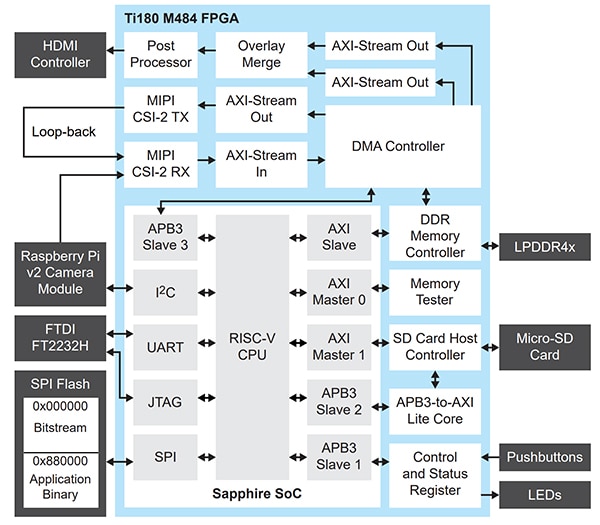

Z punktu widzenia koncepcji, projekt referencyjny (ilustracja 1) odbiera obrazy z kilku kamer z interfejsem mobilnego procesora przemysłowego (MIPI), wykonuje buforowanie klatek w pamięci LPDDR4x, a następnie wysyła obrazy do wyświetlacza High Definition Multimedia Interface (HDMI). Do obsługi wejść kamery i wyjścia (HDMI) służy karta antresolowa FPGA (FMC) i cztery interfejsy Samtec QSE.

Ilustracja 1: z punktu widzenia koncepcji, projekt referencyjny Ti180 M484 odbiera obrazy z kilku kamer MIPI, wykonuje buforowanie ramek w pamięci LPDDR4x, a następnie wysyła obrazy na wyświetlacz HDMI. >(Źródło ilustracji: Efinix)

Ilustracja 1: z punktu widzenia koncepcji, projekt referencyjny Ti180 M484 odbiera obrazy z kilku kamer MIPI, wykonuje buforowanie ramek w pamięci LPDDR4x, a następnie wysyła obrazy na wyświetlacz HDMI. >(Źródło ilustracji: Efinix)

Karta rozszerzeń FMC - QSE jest używana w połączeniu z płytką podrzędną HDMI w celu zapewnienia wyjściowego toru wideo, a trzy złącza QSE służą do podłączenia kamer MIPI DFRobot SEN0494. Jeśli nie ma dostępnych wielu kamer MIPI, można użyć pojedynczej kamery, zapętlając jej kanał w celu symulacji dodatkowych kamer.

Na wysokim poziomie to zastosowanie może wydawać się proste. Jednak wyzwaniem jest odbieranie wielu strumieni interfejsu MIPI w wysokiej rozdzielczości (HD) z dużą liczbą klatek na sekundę. Właśnie tutaj technologia FPGA jest przydatna, ponieważ umożliwia projektantom równoległą obsługę wielu strumieni MIPI.

Architektura projektu referencyjnego wykorzystuje struktury przetwarzania równoległego i sekwencyjnego przez układ bezpośrednio programowalnej macierzy bramek (FPGA). Struktury równoległe służą do realizacji potoku przetwarzania obrazu, a procesor RISC-V zapewnia przetwarzanie sekwencyjne używane do tablicowania (LUT) w macierzy FPGA.

W wielu systemach przetwarzania obrazu opartych na macierzach FPGA potok przetwarzania obrazu można podzielić na dwa elementy, a mianowicie strumienie wejściowe i wyjściowe. Strumień wejściowy jest podłączony do interfejsu kamera/czujnik, a funkcje przetwarzania są realizowane na sygnale wyjściowym czujnika. Funkcje te mogą obejmować konwersję Bayera, automatyczny balans bieli i inne ulepszenia. W strumieniu wyjściowym obraz jest przygotowywany do wyświetlenia. Obejmuje to zmianę przestrzeni kolorów (np. RGB na YUV) i przetwarzanie końcowe dla żądanego formatu wyjściowego, takiego jak HDMI.

Często ciąg przetwarzania obrazu wejściowego działa z częstotliwością zegara taktowania pikseli czujnika. Jest to inne taktowanie niż dla łańcucha wyjściowego, który jest przetwarzany z częstotliwością wyświetlania.

Bufor ramek służy do łączenia potoku przetwarzania wejściowego z wyjściowym i jest często przechowywany w pamięci zewnętrznej o wysokiej wydajności, takiej jak LPDDR4x. Bufor ramek odsprzęga potok wejściowy od wyjściowego, umożliwiając dostęp do bufora ramek przez bezpośredni dostęp do pamięci z odpowiednią częstotliwością zegara.

Projekt referencyjny Ti180 wykorzystuje podobne podejście do koncepcji przedstawionych powyżej. Potok przetwarzania obrazu wejściowego implementuje rdzeń przetwarzania obrazu (IP) odbiornika MIPI Camera Serial Interface 2 (CSI-2), który jest zbudowany na obsługującym warstwę fizyczną MIPI (MIPI D-PHY) wejściu-wyjściu (I/O) macierzy Titanium FPGA Titanium. MIPI jest interfejsem stwarzającym wyzwania, ponieważ oprócz komunikacji o niskiej i dużej szybkości wykorzystuje zarówno sygnalizację jednostronną, jak i różnicową na tej samej parze różnicowej. Integracja warstwy fizycznej MIPI D-PHY na wejściu-wyjściu bezpośrednio programowalnej macierzy bramek (FPGA) zmniejsza złożoność projektu karty, jednocześnie skracając wykaz materiałów (BOM).

Po odebraniu strumienia obrazów z kamery projekt referencyjny konwertuje sygnał wyjściowy interfejsu mobilnego procesora przemysłowego MIPI CSI-2 RX na strumień Advanced eXtensible Interface (AXI). Strumień AXI to jednokierunkowy szybki interfejs, który przesyła strumień danych z urządzenia nadrzędnego do urządzenia podrzędnego. Dostarczane są sygnały uzgadniania przesyłania między urządzeniem nadrzędnym a podrzędnym (tvalid i tready) wraz z sygnałami wstęgi bocznej. Sygnały wstęgi bocznej mogą służyć do przekazywania informacji o taktowaniu obrazu, takich jak początek ramki i koniec linii.

Strumień AXI Stream jest idealny do zastosowań związanych z przetwarzaniem obrazu i umożliwia firmie Efinix udostępnianie różnorodnej własności intelektualnej (IP) rozwiązań do przetwarzania obrazu, które można następnie łatwo zintegrować z łańcuchem przetwarzania zgodnie z wymaganiami zastosowania.

Po odebraniu dane obrazu MIPI CSI-2 i sygnały taktowania są konwertowane na strumień AXI i wprowadzane do modułu bezpośredniego dostępu do pamięci (DMA), który zapisuje ramkę obrazu w pamięci LPDDR4x i działa jako bufor ramek.

Moduł DMA działa pod kontrolą rdzenia RISC-V w bezpośrednio programowalnej macierzy bramek (FPGA) w układzie SoC Sapphire. Układ SoC zapewnia kontrolę, taką jak zatrzymywanie i rozpoczynanie zapisu DMA, a ponadto dostarcza kanałowi zapisu DMA informacje niezbędne do prawidłowego zapisu danych obrazu w pamięci LPDDR4x. Obejmuje to informacje o miejscu w pamięci oraz szerokość i wysokość obrazu wyrażoną w bajtach.

Kanał wyjściowy w projekcie referencyjnym odczytuje informacje o obrazie z bufora ramek LPDDR4x pod kontrolą układu SoC RISC-V. Dane są wyprowadzane z DMA IP jako strumień AXI, który jest następnie konwertowany z formatu RAW przesyłanego przez czujnik do formatu RGB (ilustracja 2) i przygotowywany do wyjścia przez wbudowany nadajnik HDMI ADV7511 firmy Analog Devices.

Ilustracja 2: przykładowe obrazy generowane przez projekt referencyjny. (Źródło ilustracji: Adam Taylor)

Ilustracja 2: przykładowe obrazy generowane przez projekt referencyjny. (Źródło ilustracji: Adam Taylor)

Użycie funkcji bezpośredniego dostępu do pamięci (DMA) również umożliwia układowi SoC RISC-V Sapphire uzyskiwanie dostępu do obrazów zapisanych w buforze ramek i skróconych statystyk oraz informacji o obrazie. Układ SoC Sapphire jest również w stanie zapisywać nakładki w pamięci LPDDR4x, dzięki czemu można je łączyć z wyjściowym strumieniem wideo.

Nowoczesne sensory obrazu CMOS (CIS) mają kilka trybów działania i można je skonfigurować tak, aby zapewniały przetwarzanie wewnątrzukładowe oraz kilka różnych formatów wyjściowych i schematów taktowania. Ta konfiguracja jest zwykle realizowana przez interfejs I²C. W projekcie referencyjnym firmy Efinix łączność I²C z kamerami MIPI jest zapewniana przez procesor RISC-V w układzie SoC Sapphire.

Integracja procesora RISC-V z bezpośrednio programowalną macierzą bramek (FPGA) Titanium zmniejsza całkowite rozmiary ostatecznego rozwiązania, ponieważ eliminuje potrzebę implementacji zarówno złożonych maszyn stanowych FPGA, które zwiększają ryzyko projektowe, jak i zewnętrznych procesorów, które wydłużają wykaz materiałów (BOM).

Dołączenie procesora umożliwia również obsługę dodatkowej własności intelektualnej (IP) do komunikacji z kartą MicroSD. Umożliwia to użycie w rzeczywistych zastosowaniach, w których może być wymagane przechowywanie obrazów do późniejszej analizy.

Ogólnie rzecz biorąc, architektura projektu referencyjnego Ti180 została zoptymalizowana, aby umożliwić kompaktowe, niedrogie, a jednocześnie wydajne rozwiązanie, które pozwala deweloperom obniżyć koszty wykazu materiałów (BOM) przez integrację systemu.

Jedną z kluczowych zalet projektów referencyjnych jest to, że można ich używać do szybkiego rozpoczęcia tworzenia aplikacji na niestandardowym sprzęcie, umożliwiając deweloperom wykorzystanie krytycznych elementów projektu i rozbudowanie go dostosowując odpowiednio. Obejmuje to możliwość wykorzystania przepływu TinyML Efinix do wdrażania zastosowań wizyjnych TinyML działających w macierzy FPGA. Możliwe jest również wykorzystanie zarówno równoległego charakteru logiki FPGA, jak i możliwości łatwego dodawania niestandardowych instrukcji do procesorów RISC-V, co pozwala na tworzenie akceleratorów w logice FPGA.

Implementacja

Jak omówiono w części 1, architektura Efinix jest wyjątkowa, ponieważ wykorzystuje komórki eXchangeable Logic and Routing (XLR) w celu zapewnienia zarówno funkcji routingu, jak i logiki. System wideo, taki jak projekt referencyjny, jest systemem mieszanym, wymagającym zarówno logiki, jak i routingu: do zaimplementowania funkcji przetwarzania obrazu wymagana jest rozbudowana logika, a do połączenia komórek przetwarzania obrazu na wymaganych częstotliwościach potrzebny jest rozbudowany routing.

Projekt referencyjny wykorzystuje około 42% komórek XLR w urządzeniu, pozostawiając dużo miejsca na dodatki, w tym niestandardowe aplikacje, takie jak brzegowe uczenie maszynowe (ML).

Wykorzystanie bloku pamięci RAM i bloków cyfrowego przetwarzania sygnału (DSP) jest również bardzo wydajne, wykorzystywane jest tylko 4 z 640 bloków DSP i 40% bloków pamięci (ilustracja 3).

|

Ilustracja 3: alokacja zasobów w architekturze Efinix pokazuje, że wykorzystywane jest tylko 42% komórek XLR, pozostawiając dużo miejsca na dodatkowe procesy. (Źródło ilustracji: Adam Taylor)

Na wejściu-wyjściu urządzenia znajduje się interfejs DDR pamięci LPDDR4x, który służy do zapewniania pamięci aplikacji dla układu SoC Sapphire i buforów ramek obrazu. Wszystkie zasoby MIPI dedykowane dla urządzenia są wykorzystywane razem z 50% pętli synchronizacji fazowej (ilustracja 4).

|

Ilustracja 4: wygląd interfejsu i używanych zasobów wejścia-wyjścia. (Źródło ilustracji: Adam Taylor)

Wejście-wyjście ogólnego przeznaczenia (GPIO) służy do zapewnienia komunikacji I²C wraz z kilkoma interfejsami podłączonymi do układu SoC Sapphire, w tym NOR FLASH, USB UART i kartą SD. Wejście-wyjście HSIO dostarcza sygnałów wyjściowych wysokich prędkości do nadajnika HDMI ADC7511.

Jednym z kluczowych elementów podczas projektowania z bezpośrednio programowalnymi macierzami bramek (FPGA) jest nie tylko wdrożenie i dopasowanie projektu w macierzy FPGA, ale także możliwość umieszczenia projektu logicznego w macierzy FPGA i osiągnięcia wymaganej wydajności taktowania podczas kierowania przepływem.

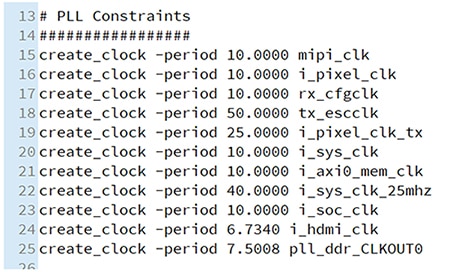

Dawno minęły czasy projektów FPGA z pojedynczą domeną zegara. W projekcie referencyjnym Ti180 istnieje kilka różnych zegarów pracujących na wysokich częstotliwościach. Ostateczna tabela taktowania pokazuje maksymalne częstotliwości osiągnięte dla zegarów w systemie. W tym miejscu wymagane parametry działania taktowania mogą być również widoczne w ograniczeniach (ilustracja 5), w których określono maksymalną częstotliwość zegara 148,5MHz dla zegara wyjściowego HDMI.

Ilustracja 5: ograniczenia zegara dla projektu referencyjnego. (Źródło ilustracji: Adam Taylor)

Ilustracja 5: ograniczenia zegara dla projektu referencyjnego. (Źródło ilustracji: Adam Taylor)

Implementacja taktowania w kontekście ograniczeń pokazuje potencjał struktury Titanium FPGA XLR, ponieważ zmniejsza możliwe opóźnienia routingu, podwyższając w ten sposób parametry działania projektu (ilustracja 6).

|

Ilustracja 6: implementacja taktowania w kontekście ograniczeń pokazuje potencjał struktury Titanium FPGA XLR, ponieważ zmniejsza możliwe opóźnienia routingu, podwyższając w ten sposób parametry działania projektu. (Źródło ilustracji: Adam Taylor)

Podsumowanie

Projekt referencyjny Ti180 M484 znakomicie demonstruje możliwości macierzy FPGA firmy Efinix, a w szczególności Ti180. Projekt wykorzystuje kilka unikalnych struktur wejścia-wyjścia do implementacji złożonej ścieżki przetwarzania obrazu, która obsługuje kilka przychodzących strumieni MIPI. Ten system przetwarzania obrazu działa pod kontrolą układu SoC Sapphire z programowalnym rdzeniem, który implementuje niezbędne elementy przetwarzania sekwencyjnego w danym zastosowaniu.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.