Podstawy syntezatorów częstotliwości z pętlą synchronizacji fazowej

Przekazane przez: Północnoamerykańscy redaktorzy DigiKey

2021-02-03

Rosnące szybkości transmisji danych w szybkich magistralach komunikacji szeregowej wymagają zegarów systemowych o wyższych częstotliwościach, doskonałej stabilności, większej rozdzielczości częstotliwości i większej czystości sygnału. Takie właściwości oferują bezpośrednie syntezatory cyfrowe, ale tylko przy częstotliwościach poniżej 2 lub 3GHz. Potrzebne jest rozwiązanie dla częstotliwości dochodzących do kilkudziesięciu gigaherców.

Rozwiązanie to rozpoczyna się od analogowych syntezatorów częstotliwości opartych na pętli synchronizacji fazowej (PLL), które generują częstotliwości zegarowe do 30GHz. Następnie syntezatory z podziałem całkowitym (Integer-N, które mnożą częstotliwość referencyjną przez liczbę całkowitą) i syntezatory z podziałem ułamkowym (Fractional N które mnożą częstotliwość referencyjną przez niecałkowite wartości ułamkowe) wykorzystują specjalne techniki, które minimalizują szum fazowy i podobne zakłócenia sygnału.

W tym artykule opisano budowę syntezatorów częstotliwości zarówno z podziałem całkowitym (Integer-N), jak i ułamkowym (Fractional-N), na przykładzie urządzeń firmy Analog Devices. W artykule podkreślono również innowacje, które umożliwiają stosowanie tych urządzeń w szeregowych łączach danych wysokiej prędkości, a także w radarach o zmiennej częstotliwości.

Syntezatory z pętlą synchronizacji fazowej z podziałem całkowitym (Integer-N)

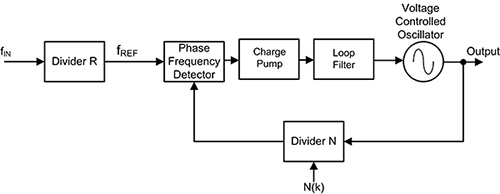

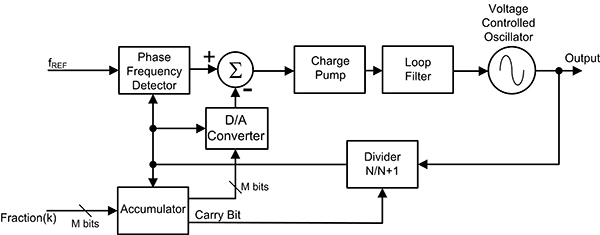

Obwody PLL służą do sterowania częstotliwości i fazy. Mogą być skonfigurowane jako źródła zegarów, powielacze częstotliwości, demodulatory, generatory śledzące lub obwody odzyskiwania zegara. Każde z tych zastosowań wymaga innej charakterystyki, ale wszystkie wykorzystują tę samą podstawową koncepcję obwodu. Ilustracja 1 przedstawia schemat blokowy podstawowego syntezatora PLL skonfigurowanego jako powielacz częstotliwości.

Ilustracja 1: schemat blokowy klasycznego syntezatora częstotliwości z pętlą synchronizacji fazowej z podziałem całkowitym (Integer-N). (Źródło ilustracji: DigiKey)

Ilustracja 1: schemat blokowy klasycznego syntezatora częstotliwości z pętlą synchronizacji fazowej z podziałem całkowitym (Integer-N). (Źródło ilustracji: DigiKey)

Działanie tego obwodu jest typowe dla wszystkich pętli synchronizacji fazowej. Jest to w zasadzie układ sterowania sprzężeniem zwrotnym, który steruje fazą oscylatora sterowanego napięciem (VCO). Sygnał wejściowy jest podawany do dzielnika wstępnego (preskalera), który dzieli częstotliwość wejściową przez współczynnik R. Na wyjściu preskalera pojawia się częstotliwość referencyjna, która stanowi jeden z sygnałów wejściowych detektora częstotliwościowo-fazowego (PFD).

Drugim sygnałem wejściowym detektora PFD jest sygnał sprzężenia zwrotnego z wyjścia licznika dzielenia przez N. Zwykle jeśli syntezator PLL jest zablokowany, częstotliwości obu sygnałów będą prawie takie same. Sygnałem wyjściowym detektora fazy jest napięcie proporcjonalne do różnicy faz między dwoma wejściami. Jeśli pętla jest odblokowana, jak to ma miejsce podczas uruchamiania lub gdy występuje duże chwilowe przesunięcie częstotliwości na wejściu, wówczas detektor częstotliwościowo-fazowy działa w celu doprowadzenia częstotliwości roboczej PLL do żądanego ustawienia. Po osiągnięciu tej częstotliwości detektor PFD powraca do trybu detektora fazy, a jego sygnał wyjściowy jest proporcjonalny do różnicy faz między częstotliwością referencyjną i sygnałem sprzężenia zwrotnego.

Detektor częstotliwościowo-fazowy steruje pompą ładunku, która jest przełączanym bipolarnie źródłem prądowym. Oznacza to, że może wysyłać dodatnie i ujemne impulsy prądu do filtra pętli syntezatora PLL.

Filtr pętli wygładza sygnał błędu fazy, a także określa charakterystykę dynamiczną syntezatora PLL. Przefiltrowany sygnał steruje oscylatorem sterowanym napięciem (VCO). Należy zauważyć, że sygnał wyjściowy oscylatora sterowanego napięciem (VCO) ma częstotliwość, która jest N-krotnością sygnału wejściowego podanego na wejście referencyjne częstotliwości do detektora częstotliwościowo-fazowego i jest równy N/R-krotności częstotliwości wejściowej. Ten sygnał wyjściowy jest przesyłany z powrotem do detektora fazy za pomocą licznika dzielenia przez N.

Zwykle filtr pętli jest zaprojektowany tak, aby pasował do charakterystyk zależnych od zastosowania syntezatora PLL. Jeśli syntezator PLL ma odbierać i śledzić sygnał, szerokość pasma filtra pętli będzie większa niż w przypadku, gdyby odbierana miała być stała częstotliwość wejściowa. Zakres częstotliwości, który syntezator PLL zaakceptuje i na którym będzie zablokowany, nazywany jest „zakresem przechwytywania”. Gdy syntezator PLL jest zablokowany i śledzi sygnał, zakres częstotliwości, które będzie śledzić, nazywany jest „zakresem śledzenia”. Co do zasady zakres śledzenia jest większy niż zakres przechwytywania. Filtr pętli syntezatora PLL określa również maksymalną szybkość narastania/opadania, czyli, jak szybko częstotliwość sygnału może zmieniać się bez utraty blokady. Im węższe pasmo filtra pętli, tym mniejszy możliwy do osiągnięcia błąd fazy. Dzieje się to kosztem wolniejszej reakcji i zmniejszonego zakresu przechwytywania. Syntezatory PLL używane w zastosowaniach zegarowych działają głównie na stałych częstotliwościach. Ogólnie szerokość pasma filtra pętli powinna być znacznie niższa niż częstotliwość referencyjna.

Ponieważ częstotliwość wyjściowa syntezy PLL jest całkowitoliczbową wielokrotnością częstotliwości referencyjnej, ich rozdzielczości są równe. Uzyskanie dokładniejszej rozdzielczości częstotliwości wymaga zmniejszenia częstotliwości referencyjnej, co odbywa się za pomocą licznika wstępnego R.

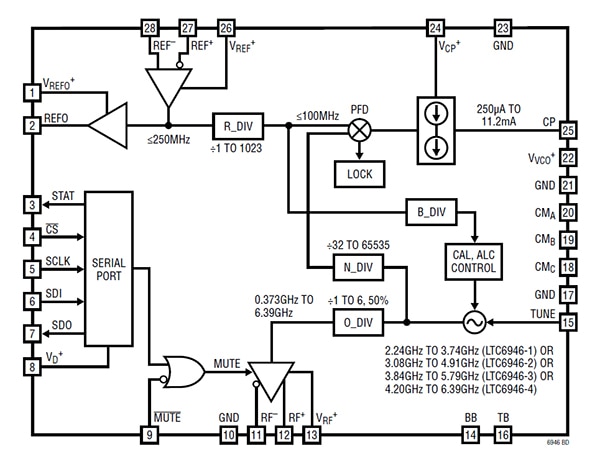

Przykładem dostępnego na rynku syntezatora częstotliwości z podziałem całkowitym (Integer-N) jest układ LTC6946IUFD-3#PBF firmy Analog Devices, czyli niskoszumowy syntezator o częstotliwości od 0,64 do 5,790GHz ze zintegrowanym oscylatorem sterowanym napięciem (VCO) i doskonałymi parametrami w zakresie zafałszowań (ilustracja 2). Jest produktem należącym do grupy czterech układów scalonych syntezatorów (każdy o innym zakresie częstotliwości) obejmującej całkowity zakres od 0,373 do 6,390GHz.

Ilustracja 2: schemat blokowy syntezatora częstotliwości z podziałem całkowitym (Integer-N) LTC6946IUFD-3#PBF ze zintegrowanym oscylatorem sterowanym napięciem (VCO) firmy Analog Devices. (Źródło ilustracji: Analog Devices)

Ilustracja 2: schemat blokowy syntezatora częstotliwości z podziałem całkowitym (Integer-N) LTC6946IUFD-3#PBF ze zintegrowanym oscylatorem sterowanym napięciem (VCO) firmy Analog Devices. (Źródło ilustracji: Analog Devices)

Ten syntezator wymaga zewnętrznego filtra pętli zapewnianego przez użytkownika z możliwością optymalizacji pod kątem określonego zastosowania. Wewnętrzny dzielnik wstępny (preskaler) ma zakres dzielenia od 1 do 1023. Dzielnik pętli ma zakres od 32 do 65535. Natężenie prądu pompy ładunku można dostosować zależnie od wymagań filtra pętli, regulując je w zakresie od 250μA do 11,2mA.

Syntezatory z pętlą synchronizacji fazowej z podziałem ułamkowym (Fractional-N)

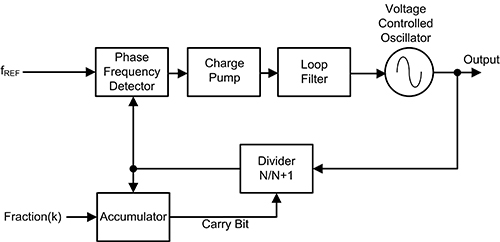

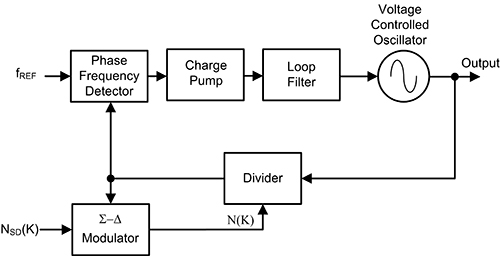

Rozdzielczość częstotliwości syntezatora PLL można poprawić zmniejszając wielkość przeskoku do wartości mniejszych niż wartości całkowite, tj. wprowadzając w dzielniku pętli (N) przeskoki ułamkowe. Odbywa się to poprzez dynamiczne zmienianie lub rozpraszanie wartości odliczania. Oznacza to, że w ustawieniu dzielnika wartość N jest utrzymywana przez ustaloną liczbę cykli częstotliwości wyjściowej syntezatora PLL i jest okresowo zwiększana do innej wartości, takiej jak N+1. Na przykład, jeśli nastawa dzielnika wynosi 4 dla trzech okresów referencyjnych i 5 dla czwartego cyklu referencyjnego, to efektywne odliczanie wynosi 4,25. Jednym ze sposobów osiągnięcia tego jest użycie akumulatora, jak pokazano na ilustracji 3.

Ilustracja 3: schemat blokowy syntezatora PLL z podziałem ułamkowym (Fractional-N) wykorzystującego akumulator do modulowania liczby dzielnika. (Źródło ilustracji: DigiKey)

Ilustracja 3: schemat blokowy syntezatora PLL z podziałem ułamkowym (Fractional-N) wykorzystującego akumulator do modulowania liczby dzielnika. (Źródło ilustracji: DigiKey)

Akumulator zlicza impulsy wyjściowe z dzielnika i każde M, gdzie M jest współczynnikiem akumulatora. Następnie wysyła bit przenoszenia, który zmienia wejście dzielnika. Ilustracja 4 dalej pokazuje przykład nastawy dzielnika ułamkowego na poziomie 4,25.

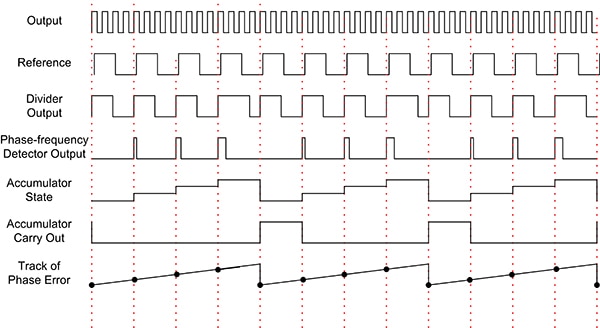

Ilustracja 4: schemat taktowania dla syntezatora z podziałem ułamkowym (Fractional-N) wykorzystującego akumulator. (Źródło ilustracji: DigiKey)

Ilustracja 4: schemat taktowania dla syntezatora z podziałem ułamkowym (Fractional-N) wykorzystującego akumulator. (Źródło ilustracji: DigiKey)

Akumulator jest sterowany podzielonym sygnałem wyjściowym i liczy modulo cztery, tj. M jest równe cztery. Co czwarty impuls generuje wyjście przeniesienia, które zwiększa liczbę dzielnika o jeden. Akumulator resetuje się i zaczyna liczyć ponownie. Zwiększenie nastawy dzielnika powoduje przesunięcie częstotliwości wyjściowej, co powoduje skumulowany błąd przesunięcia fazy. Ścieżka błędu fazy pokazuje wartość impulsu w funkcji czasu.

Średnia nastawa dzielnika wynosi 4,25, ale wyjście syntezatora jest modulowane fazowo, co skutkuje zafałszowanymi sygnałami na wyjściu. Patrząc na stan akumulatora widać, że śledzi on błąd fazy. Można to wykorzystać do usunięcia modulacji, jak pokazano na ilustracji 5.

Ilustracja 5: wykorzystanie stanu akumulatora po konwersji cyfrowo-analogowej do anulowania modulacji fazy z powodu rozpraszania ułamkowego (Fractional-N). (Źródło ilustracji: DigiKey)

Ilustracja 5: wykorzystanie stanu akumulatora po konwersji cyfrowo-analogowej do anulowania modulacji fazy z powodu rozpraszania ułamkowego (Fractional-N). (Źródło ilustracji: DigiKey)

Stan akumulatora jest konwertowany z cyfrowego na analogowy przez przetwornik cyfrowo-analogowy (D/A) i skalowany, a następnie odejmowany od sygnału wyjściowego detektora częstotliwościowo-fazowego w celu anulowania modulacji fazy z powodu rozpraszania ułamkowego (Fractional-N). Procedurę te należy przeprowadzać z wielką starannością; jeśli sygnał korekcyjny nie pasuje idealnie do błędu fazy, na wyjściu pojawią się zafałszowane sygnały.

Wprowadzanie modulatora sigma-delta

Przyczyną zafałszowanych sygnałów wyjściowych z syntezatora jest okresowość w akumulatorze. Jeśli akumulator zostanie zastąpiony modulatorem sigma-delta, wówczas, aby zminimalizować zafałszowane odpowiedzi i szumy, do modulacji liczby dzielnika można zastosować techniki cyfrowe. Takie zastąpienie pokazano na ilustracji 6.

Ilustracja 6: zastąpienie akumulatora modulatorem sigma-delta pozwala na zmianę liczby dzielnika w celu ograniczenia zafałszowań odpowiedzi technikami cyfrowymi. (Źródło ilustracji: DigiKey)

Ilustracja 6: zastąpienie akumulatora modulatorem sigma-delta pozwala na zmianę liczby dzielnika w celu ograniczenia zafałszowań odpowiedzi technikami cyfrowymi. (Źródło ilustracji: DigiKey)

W topologii modulacji sigma-delta istnieją tak naprawdę dwie popularne techniki cyfrowe. Pierwsza polega na zwiększeniu liczby dzielnika N w szerszym zakresie wartości, tak aby średni współczynnik podziału dał pożądaną wartość dzielnika ułamkowego. Pozwala ona na zmniejszenie pierwotnego zafałszowania ułamkowego. Syntezator oparty na akumulatorze zmienia liczbę między dwoma stanami. Jest to metoda modulacji pierwszego rzędu. Syntezator PLL sigma-delta n-tego rzędu z podziałem ułamkowym moduluje licznik N między 2n różne wartości. Na przykład: modulator trzeciego rzędu będzie przełączał się między ośmioma różnymi wartościami dzielnika, a modulator czwartego rzędu zmieniałby się między 16 różnymi wartościami dzielnika.

Druga technika cyfrowa - nazywana również rozpraszaniem - polega na randomizacji sekwencji 2N tak, aby była pseudolosowa. Utrzymując średni ułamkowy współczynnik dzielnika, pozwala na konwersję zafałszowań ułamkowych na ukształtowany szum losowy w taki sposób, aby możliwe było jego odfiltrowanie syntezatorem PLL.

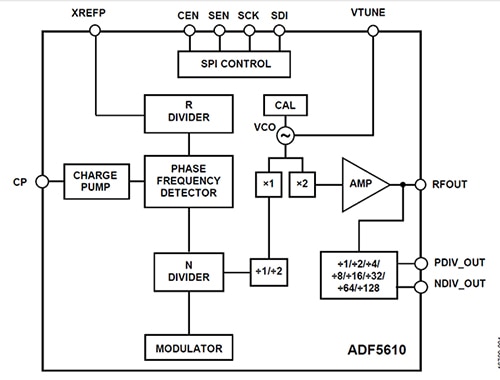

Przykładem dostępnego na rynku syntezatora sigma-delta z podziałem ułamkowym (Integer-N) jest układ ADF5610BCCZ firmy Analog Devices, który jest niskoszumowym syntezatorem z podziałem ułamkowym (Integer-N) o częstotliwości od 0,57MHz do 14,6GHz ze zintegrowanym oscylatorem sterowanym napięciem (VCO) (ilustracja 7).

Ilustracja 7: schemat blokowy syntezatora ADF5610BCCZ firmy Analog Devices, który można skonfigurować zarówno do podziału ułamkowego (Fractional-N), jak i całkowitego (Integer-N). (Źródło ilustracji: Analog Devices)

Ilustracja 7: schemat blokowy syntezatora ADF5610BCCZ firmy Analog Devices, który można skonfigurować zarówno do podziału ułamkowego (Fractional-N), jak i całkowitego (Integer-N). (Źródło ilustracji: Analog Devices)

Syntezator ADF5610 wymaga zewnętrznego oscylatora referencyjnego i filtra pętli. Posiada on zintegrowany oscylator sterowany napięciem (VCO) o częstotliwości podstawowej od 3650MHz do 7300MHz. Częstotliwości te są wewnętrznie podwajane i kierowane do wtyku RFOUT. Syntezator posiada wyjście różnicowe, które pozwala na podzielenie podwojonej częstotliwości oscylatora sterowanego napięciem (VCO) przez współczynniki 1, 2, 4, 8, 16, 32, 64 lub 128, co z kolei pozwala na generowanie częstotliwości wyjściowych RF nawet 57MHz.

Syntezator ADF5610 wykorzystuje zaawansowany modulator sigma-delta z 24-bitowym współczynnikiem ułamkowym, który osiąga wyjątkowo niskie poziomy zafałszowań. Podobnie jak we wszystkich syntezatorach wykorzystujących modulator sigma-delta, urządzenie to wykorzystuje techniki cyfrowego przetwarzania sygnału, aby znaleźć pożądany średni dzielnik ułamkowy. Proces ten, przy taktowaniu z częstotliwością detektora częstotliwościowo-fazowego (PFD), generuje wyjściowy szum modulacji zwany szumem kwantyzacji z górnoprzepustową charakterystyką częstotliwościową. Zewnętrzny dolnoprzepustowy filtr pętli służy do filtrowania szumu kwantyzacji do poziomu poniżej szumu fazowego oscylatora sterowanego napięciem (VCO), zapobiegając w ten sposób zwiększeniu ogólnego szumu fazowego układu.

Syntezator ADF5610 ma również tryb częstotliwości dokładnej dla błędu częstotliwości 0Hz. Ten tryb pozwala na wygenerowanie dokładnych częstotliwości między sąsiednimi całkowitymi krokami granicznymi N, nadal wykorzystując pełny 24-bitowy współczynnik akumulatora fazowego. Umożliwia to osiągnięcie dokładnych kroków częstotliwości z wysokim współczynnikiem porównawczym detektora fazy, umożliwiając syntezatorowi PLL utrzymanie doskonałego szumu fazowego i zafałszowań działania w tym trybie.

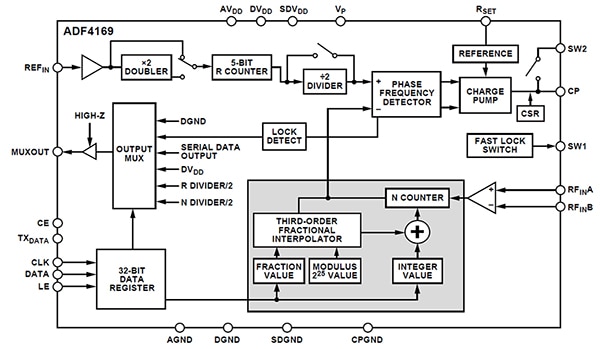

Syntezator ADF4169CCPZ-RL7 firmy Analog Devices to kolejny syntezator PLL, który można skonfigurować zarówno do pracy z podziałem całkowitym (Integer-N), jak i ułamkowym (Fractional-N). Działa on w paśmie częstotliwości radiowych do 13,5GHz z modulacją i generowaniem przebiegów. Wykorzystuje zewnętrzne wejście częstotliwości referencyjnej, oscylator sterowany napięciem (VCO) i filtr pętli. Posiada modulator sigma-delta trzeciego rzędu do syntezy ułamkowej (Fractional-N), który można wyłączyć, umożliwiając pracę urządzenia w trybie całkowitym (Integer-N) (ilustracja 8).

Ilustracja 8: syntezator ADF4169CCPZ-RL7 firmy Analog Devices wykorzystuje modulator sigma-delta trzeciego rzędu. (Źródło ilustracji: Analog Devices)

Ilustracja 8: syntezator ADF4169CCPZ-RL7 firmy Analog Devices wykorzystuje modulator sigma-delta trzeciego rzędu. (Źródło ilustracji: Analog Devices)

Syntezator ADF4158WCCPZ-RL7 jest przeznaczony do użytku w radarach fal ciągłych z modulacją częstotliwościową (FMCW). Jest w stanie generować różne typy modulowanych przebiegów w dziedzinie częstotliwości, w tym przebiegi piłokształtne i trójkątne. Jest to specjalna funkcja, która jest niezbędna w zastosowaniach radarowych.

Podsumowanie

Rosnące szybkości transmisji danych w szybkich magistralach komunikacji szeregowej wymagają od projektantów spojrzenia poza bezpośrednie syntezatory cyfrowe - które działają najlepiej poniżej 3GHz - jeśli chodzi o rozwiązania zegarowe. Syntezatory częstotliwości oparte na technologii PLL, wykorzystujące topologie podziału całkowitego (Integer-N) i ułamkowego (Fractional-N), zapewniają stabilne sygnały o niskim poziomie szumów dla zegara o wysokiej częstotliwości, komunikacji szeregowej i zastosowań radarowych w przypadku częstotliwości do kilkudziesięciu gigaherców.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.