Szybkie tworzenie zegarów wysokiej częstotliwości o niskich fluktuacjach za pomocą modułu pętli translacji

Przekazane przez: Północnoamerykańscy redaktorzy DigiKey

2021-08-04

Projektanci oprzyrządowania i systemów pomiarowych wymagają wolnych od zakłóceń sygnałów o niskich fluktuacjach, aby zapewnić stosunek sygnału do szumu (SNR) lub wielkość wektora błędu (EVM) wymagane do spełnienia rosnących wymagań klientów. W tym samym czasie są oni również pod dużą presją, aby zredukować powierzchnię płytki, a także koszty i złożoność projektowania. Ta ostatnia kwestia ma kluczowe znaczenie dla skrócenia czasu prac rozwojowych, aby móc zmieścić się w coraz krótszych terminach wprowadzenia produktu na rynek.

Aby sprostać wielu wyzwaniom związanym z zastosowaniami, inżynierowie muszą przestawić się z tradycyjnie niestandardowych dyskretnych projektów na bardziej zintegrowane rozwiązania zegarów do oprzyrządowania i pomiarów. Ważnym krokiem w tym kierunku jest zastosowanie zintegrowanej pętli translacji ze sprzężeniem fazowym (PLL). Pozwala to na konwersję częstotliwości sygnału tradycyjnego oscylatora sterowanego napięciem (VCO) w górę, przy jednoczesnym zachowaniu fluktuacji i szumu fazowego stałego zewnętrznego oscylatora lokalnego (LO).

W niniejszym artykule omówiono rolę pętli translacji w osiąganiu najniższego w branży zintegrowanego szumu fazowego. W artykule przedstawiono przykładowy system pętli translacji w jednej obudowie (SiP TL) ADF4401A firmy Analog Devices i pokazano, w jaki sposób spełnia on wymagania dotyczące wydajności dzięki generowaniu sygnału wyjściowego przetwarzanego przez wbudowaną funkcję obniżania fluktuacji skutecznych (RMS) do wartości poniżej 10fs i ulepszonej izolacji pozwalającej na tłumienie fałszywych składowych, jednocześnie spełniając wymagania projektantów w zakresie integracji, kosztów, złożoności i czasu wprowadzenia produktu na rynek.

Tradycyjne pętle ze sprzężeniem fazowym (PLL) a operacje w pętli translacji

Podstawowym celem pętli translacji jest generowanie sygnału wyjściowego zsynchronizowanego z wejściowym sygnałem odniesienia ze znacznie zredukowanym szumem fazowym w paśmie w porównaniu z tradycyjnymi pętlami PLL.

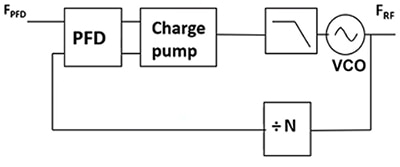

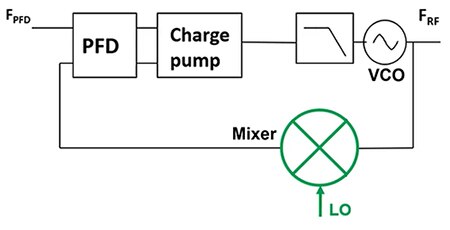

Standardowa pętla ze sprzężeniem fazowym (PLL) składa się z układu sprzężenia zwrotnego zawierającego detektor częstotliwościowo-fazowy (PFD), pompę ładunku, filtr dolnoprzepustowy (LPF), oscylator sterowany napięciem (VCO) i dzielnik N częstotliwości sprzężenia zwrotnego (ilustracja 1).

Ilustracja 1: standardowa pętla ze sprzężeniem fazowym (PLL) blokuje się na wartość odniesienia o niższej częstotliwości (FPFD) i generuje częstotliwość wyjściową (FRF). (Źródło ilustracji: Bonnie Baker)

Ilustracja 1: standardowa pętla ze sprzężeniem fazowym (PLL) blokuje się na wartość odniesienia o niższej częstotliwości (FPFD) i generuje częstotliwość wyjściową (FRF). (Źródło ilustracji: Bonnie Baker)

Detektor częstotliwościowo-fazowy porównuje fazę wejściowej wartości odniesienia i fazę sygnału sprzężenia zwrotnego oraz generuje serię impulsów proporcjonalnych do błędu fazy między nimi. Pompa ładunku odbiera impulsy detektora częstotliwościowo-fazowego i przekształca je w impulsy źródła prądowego lub odbiorowego, które z kolei dostrajają częstotliwość oscylatora sterowanego napięciem (VCO) w górę lub w dół. Filtr dolnoprzepustowy usuwa całą energię wysokiej częstotliwości impulsów i przekształca je w napięcie, które może zostać wykorzystane przez oscylator sterowany napięciem (VCO). Sygnał wyjściowy oscylatora sterowanego napięciem (VCO) jest podawany z powrotem do bloku detektora częstotliwościowo-fazowego przez dzielnik N w celu zamknięcia pętli.

Funkcja przejścia częstotliwości z ilustracji 1 jest obliczana za pomocą równania 1:

![]() Równanie 1

Równanie 1

Gdzie FRF jest częstotliwością wyjściową

N jest współczynnikiem dzielnika sprzężenia zwrotnego (może być liczbą całkowitą lub ułamkową)

FPFD jest częstotliwością detektora częstotliwościowo-fazowego (PFD)

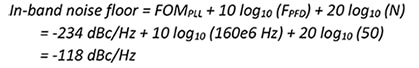

Poziom szumów wewnątrzpasmowych z ilustracji 1 oblicza się przy użyciu równania 2:

![]() Równanie 2

Równanie 2

Gdzie FOMPLL jest współczynnikiem dobroci (FOM) poziomu szumów wewnątrzpasmowych PLL

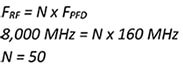

Rozważmy przykład poziomu współczynnika dobroci szumu fazowego wewnątrzpasmowego wynoszącego -234dB/Hz; częstotliwości detektora częstotliwościowo-fazowego (FPFD) 160MHz i częstotliwości wyjściowej (FRF) 8GHz.

W przypadku tego układu do obliczenia wartości N stosuje się równanie 1:

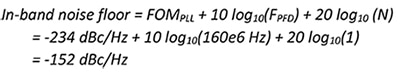

Równanie 2 służy do obliczenia poziomu szumów wewnątrzpasmowych:

W powyższych obliczeniach dzielnik N silnie przyczynia się do ogólnego poziomu szumów wewnątrzpasmowych, przy 20 log10 (50) wynoszącym 34dB. Mniejsza wartość N zmniejszyłaby poziom szumów wewnątrzpasmowych, jednak spowodowałaby również zmniejszenie częstotliwości wyjściowej. Jak więc wygenerować wysoką częstotliwość wyjściową i utrzymać niższe wzmocnienie pętli (N)?

Ilustracja 2: dla standardowej pętli ze sprzężeniem fazowym (PLL) w tym przykładzie dzielnik sprzężenia zwrotnego (20 log10(N)) charakteryzuje się o 34dB wyższym szumem wewnątrzpasmowym w porównaniu z dolnym żółtym wykresem, gdzie N = 1. (Źródło ilustracji: Bonnie Baker)

Ilustracja 2: dla standardowej pętli ze sprzężeniem fazowym (PLL) w tym przykładzie dzielnik sprzężenia zwrotnego (20 log10(N)) charakteryzuje się o 34dB wyższym szumem wewnątrzpasmowym w porównaniu z dolnym żółtym wykresem, gdzie N = 1. (Źródło ilustracji: Bonnie Baker)

Rozwiązaniem tego problemu jest zastąpienie dzielnika N stopniem mieszania z konwersją w dół (ilustracja 3).

Ilustracja 3: pętla translacji wykorzystuje mikser do konwersji częstotliwości oscylatora sterowanego napięciem (VCO) w dół do częstotliwości detektora częstotliwościowo-fazowego zamiast tradycyjnego dzielnika sprzężenia zwrotnego. (Źródło ilustracji: Bonnie Baker)

Ilustracja 3: pętla translacji wykorzystuje mikser do konwersji częstotliwości oscylatora sterowanego napięciem (VCO) w dół do częstotliwości detektora częstotliwościowo-fazowego zamiast tradycyjnego dzielnika sprzężenia zwrotnego. (Źródło ilustracji: Bonnie Baker)

Na ilustracji 3 mikser zastępuje dzielnik sprzężenia zwrotnego N, co skutkuje wzmocnieniem pętli równym 1 (N=1). Ta operacja znacznie zmniejsza udział szumów pętli sprzężenia zwrotnego w poziomie szumów wewnątrzpasmowych. Dla obliczenia szumu wewnątrzpasmowego wartość N jest teraz równa 1. Przy zastosowaniu równania 2, poziom szumów wewnątrzpasmowych dla zmodyfikowanego układu jest następujący:

Nowy szum wewnątrzpasmowy wykazuje poprawę o 34dBc/Hz.

Na ilustracji 3 mikser opiera się na oscylatorze lokalnym (LO) o skrajnie niskich szumach, zwanym skorygowanym oscylatorem lokalnym (LO). Aby osiągnąć blokadę, FLO ± FRF musi równać się FPFD.

W architekturze pętli translacji, szum fazowy skorygowanego oscylatora lokalnego (LO) jest bardzo ważny dla osiągnięcia najlepszej wydajności na wyjściu częstotliwości radiowej. Z tego powodu inżynierowie zazwyczaj projektują skorygowany oscylator lokalny (LO) w oparciu o sterowaną napięciem akustyczną falę powierzchniową (SAW), oscylatory (VCSO), generatory grzebieniowe lub oscylatory rezonatora dielektrycznego (DRO). UWAGA: Aby uzyskać pomoc przy projektowaniu skorygowanego oscylatora lokalnego (LO), należy skontaktować się z firmą Analog Devices.

Wyzwania związane z pętlą translacji

Tradycyjnie projekt niskoszumowej pętli translacji obejmuje implementację wielu bloków obwodów, co skutkuje złożonym projektem o dużych rozmiarach i ograniczonej elastyczności. Ponadto cały obwód musi zostać zweryfikowany i scharakteryzowany pod kątem docelowego działania. Na przykład jednym z głównych problemów projektowych jest upływ oscylatora lokalnego (LO) (oscylator LO - izolacja RF) do sygnału wyjściowego o częstotliwości radiowej (RF). Jest to poważne wyzwanie dla inżynierów. W przypadku tradycyjnych projektów inżynierowie zwykle stosują wiele iteracji projektowych, aby osiągnąć zoptymalizowaną wydajność i odpowiednią izolację.

Ilustracja 3 pokazuje, w jaki sposób moduł ADF4401A integruje główne bloki obwodów, aby zapewnić w pełni scharakteryzowane rozwiązanie i wyeliminować tradycyjnie problematyczne obszary związane z wydajnością i izolacją w projektach pętli translacji. Omawiane programowalne rozwiązanie umożliwia inżynierom osiągnięcie optymalnej wydajności przy pierwszej próbie i skrócenie czasu wprowadzenia produktu na rynek.

Ewaluacja modułu ADF4401A

Moduł ADF4401A został zaprojektowany, aby pomóc inżynierom skrócić czas wprowadzania na rynek oprzyrządowania o wysokich parametrach działania, wykorzystując rozwiązanie do generowania częstotliwości o szerokości pasma radiowego od 62,5MHz do 8GHz. Dzięki zastosowaniu miksera konwertującego w dół, moduł ADF4401A posiada bardzo niski poziom szumów wewnątrzpasmowych z szerokopasmowymi fluktuacjami wynoszącymi ~9fs całkowanymi w zakresie od 100Hz do 100MHz. Efektem zastosowania określonych technik projektowania i rozmieszczenia elementów w module ADF4401A jest wolny od zakłóceń zakres dynamiczny 90dBc. Obudowa o wymiarach 18x18x2,018mm znacznie zmniejsza ilość miejsca zajmowaną na płytce w porównaniu z tradycyjnym projektem dyskretnym.

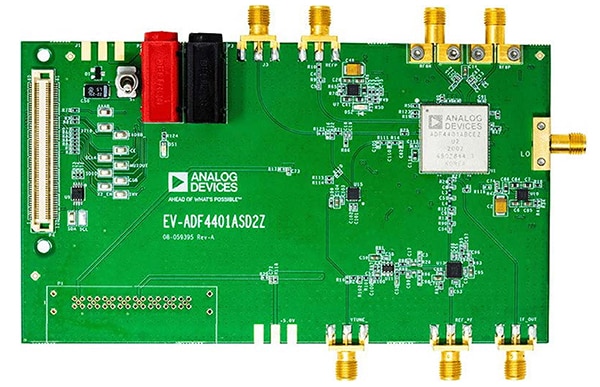

Aby ocenić parametry działania urządzenia, projektanci mogą wykorzystać płytkę ewaluacyjną EV-ADF4401ASD2Z (ilustracja 4). Płytka zawiera kompletną pętlę translacji wraz z zewnętrznym detektorem częstotliwościowo-fazowym (HMC3716), aktywnym filtrem (LT6200) i multiplekserem (ADG1609).

Ilustracja 4: płytka ewaluacyjna EV-ADF4401ASD2Z dla modułu pętli translacji ADF4401A zawiera zewnętrzny detektor częstotliwości fazowej, interfejs USB i regulatory napięcia. (Źródło ilustracji: Analog Devices)

Ilustracja 4: płytka ewaluacyjna EV-ADF4401ASD2Z dla modułu pętli translacji ADF4401A zawiera zewnętrzny detektor częstotliwości fazowej, interfejs USB i regulatory napięcia. (Źródło ilustracji: Analog Devices)

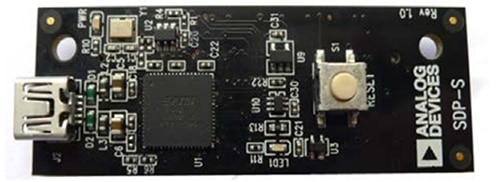

Płytka EV-ADF4401ASD2Z zawiera system pętli translacji w jednej obudowie (SiP TL) ADF4401A ze zintegrowanym oscylatorem sterowanym napięciem (VCO), filtrem pętli (5MHz), detektorem częstotliwościowo-fazowym (PFD), interfejsem USB i regulatorami napięcia. Dodatkowo płytka EV-ADF4401ASD2Z wymaga płytki kontrolera EVAL-SDP-CS1Z systemowej szeregowej platformy demonstracyjnej (SDP-S) (ilustracja 5). Płytka ta zapewnia połączenie USB między komputerem PC i płytką EV-ADF4401ASD2Z, a w rezultacie możliwość jej programowania. Płytka kontrolera nie jest elementem zestawu EV-ADF4401ASD2Z.

Ilustracja 5: płytka kontrolera EVAL-SDP-CS1Z (lub SDP-S) jest wymagana do zapewnienia połączenia USB między płytką EV-ADF4401ASD2Z i komputerem w celu programowania. (Źródło ilustracji: Analog Devices)

Ilustracja 5: płytka kontrolera EVAL-SDP-CS1Z (lub SDP-S) jest wymagana do zapewnienia połączenia USB między płytką EV-ADF4401ASD2Z i komputerem w celu programowania. (Źródło ilustracji: Analog Devices)

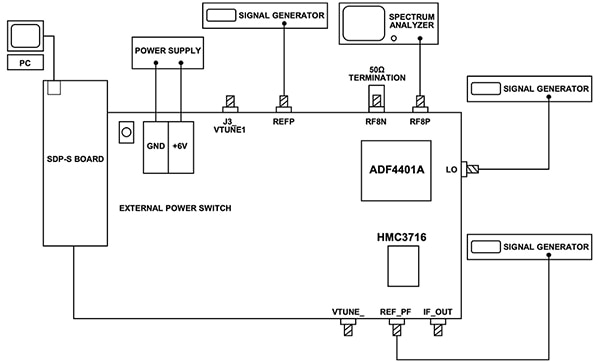

Ilustracja 6 przedstawia fizyczne połączenia systemu EV-ADF4401ASD2Z. Funkcjami TL SiP steruje powiązane oprogramowanie do analizy, kontroli i ewaluacji (ACE). Zasilanie pochodzi z zewnętrznego zasilacza o napięciu 6V.

Ilustracja 6: diagram konfiguracji płytki EV-ADF4401ASD2Z przedstawia sprzęt i połączenia wymagane do ewaluacji modułu ADF4401A, wraz z płytką sterującą SDP-S, komputerem, zasilaczem, generatorami sygnałów i analizatorem widma. (Źródło ilustracji: Analog Devices)

Ilustracja 6: diagram konfiguracji płytki EV-ADF4401ASD2Z przedstawia sprzęt i połączenia wymagane do ewaluacji modułu ADF4401A, wraz z płytką sterującą SDP-S, komputerem, zasilaczem, generatorami sygnałów i analizatorem widma. (Źródło ilustracji: Analog Devices)

Sugerowany sprzęt do użycia z tą płytką ewaluacyjną to m.in. komputer z systemem Windows, analizator widma lub analizator źródła sygnału oraz trzy generatory sygnałów.

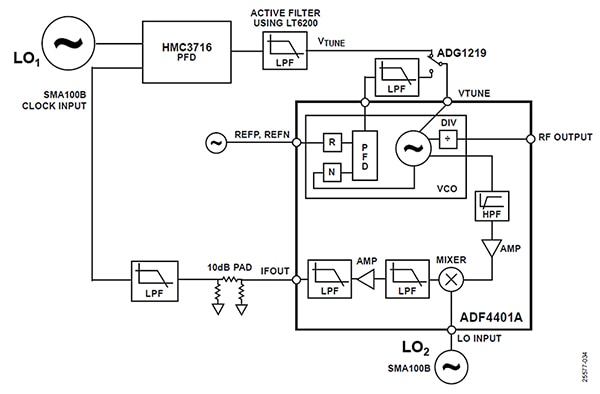

Schemat blokowy płytki ewaluacyjnej EV-ADF4401ASD2Z ukazuje moduł ADF4401A wraz z detektorem częstotliwościowo-fazowym HMC3716, wzmacniaczem operacyjnym LT6200 oraz przełącznikiem pojedynczym dwupozycyjnym (SPDT) ADG1219 firmy Analog Devices (ilustracja 7).

Rysunek 7: schemat blokowy płytki ewaluacyjnej EV-ADF4401ASD2Z przedstawia kluczowe komponenty obsługujące pętlę translacji AD4401A. (Źródło ilustracji: Analog Devices)

Rysunek 7: schemat blokowy płytki ewaluacyjnej EV-ADF4401ASD2Z przedstawia kluczowe komponenty obsługujące pętlę translacji AD4401A. (Źródło ilustracji: Analog Devices)

Niezbędne jest użycie detektora częstotliwościowo-fazowego, który może działać przy wysokich częstotliwościach, ponieważ minimalizuje to potrzebę stosowania dzielników, które mogą pogorszyć odpowiedź szumów wewnątrzpasmowych. Zdolność do porównywania faz 1,3GHz detektora częstotliwościowo-fazowego HMC3716 firmy Analog Devices czyni go idealnym do zastosowania w zakresie częstotliwości pośredniej (IF) modułu ADF4401A. Zdolność takiego obwodu do porównywania zarówno częstotliwości, jak i fazy eliminuje potrzebę stosowania dodatkowych obwodów do wysterowania częstotliwości do zamierzonej wartości wyjściowej. Detektor częstotliwościowo-fazowy HMC3716 staje się zewnętrznym elementem pozwalającym zamknąć pętlę korekcji. Zakres pracy wysokich częstotliwości i bardzo niski poziom szumów fazowych urządzenia HMC3716 umożliwiają projektowanie szerokopasmowych filtrów pętli.

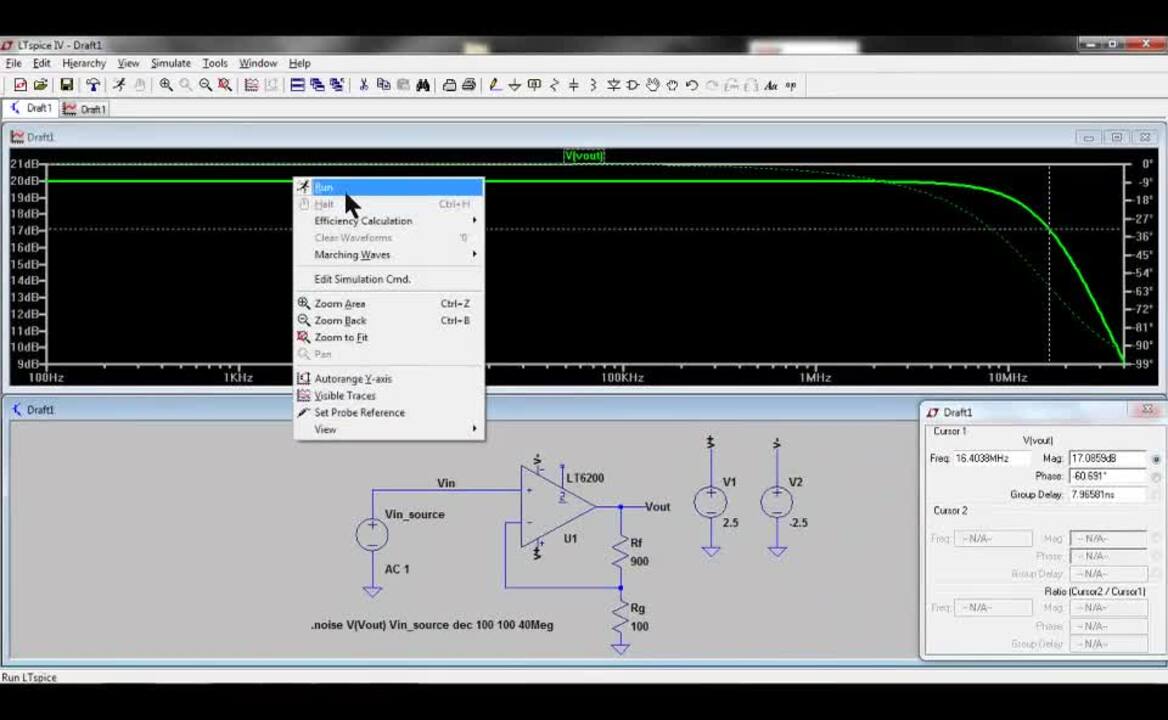

Na ilustracji 7 wzmacniacz operacyjny LT6200 w konfiguracji filtra dolnoprzepustowego (LPF) tłumi impulsy o wysokiej częstotliwości, natomiast przełącznik ADG1219 zamyka pętlę translacyjną układu.

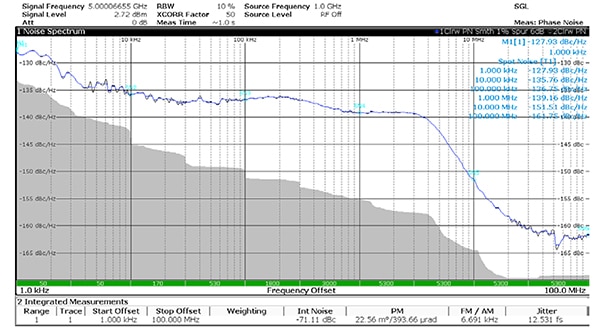

Oprawa ewaluacyjna EV-ADF4401ASD2Z tworzy wewnątrzpasmowe wykresy szumów i dokonuje pomiarów fluktuacji, jak pokazano na ilustracji 8.

Ilustracja 8: szum fazowy modulacji jednowstęgowej przy sygnale wyjściowym 5GHz, z zewnętrznym odniesieniem HMC3716 500MHz i zewnętrznym oscylatorem lokalnym (LO) 4,5GHz. (Źródło ilustracji: Analog Devices)

Ilustracja 8: szum fazowy modulacji jednowstęgowej przy sygnale wyjściowym 5GHz, z zewnętrznym odniesieniem HMC3716 500MHz i zewnętrznym oscylatorem lokalnym (LO) 4,5GHz. (Źródło ilustracji: Analog Devices)

Na ilustracji 8 oscylator lokalny LO2 i wejście HMC3716 stanowią generator sygnału RF i mikrofalowego SMA100B. Szum wewnątrzpasmowy oscylatora lokalnego LO2 płytki ewaluacyjnej jest równy ok. -135dBc/Hz, co jest widoczne przy niskich korekcjach do 300kHz. Oscylator lokalny LO2, moduł ADF4401A, detektor częstotliwościowo-fazowy HMC3716 i filtr pętli pozwalają uzyskać szum wewnątrzpasmowy na poziomie ok. -140dBc/Hz. Wewnętrzny szum fazowy pojawia się w zakresie między 5MHz a 50MHz, a poziom szumu fazowego urządzenia wynosi około -160dBc/Hz. Łącznie te wartości dają fluktuacje skuteczne (RMS) wynoszące 12,53fs.

Podsumowanie

Szybkie systemy oprzyrządowania wymagają zegarów o wyjątkowo niskich fluktuacjach, aby zapewnić bezpieczeństwo danych wyjściowych. Znalezienie odpowiednich urządzeń, które pomogą zbudować szybki gigahercowy system zegarowy jest dla inżynierów wyzwaniem. Pętla translacji ADF4401A znacznie upraszcza wybór urządzenia do budowy systemu zegarowego. Stanowi ona kompaktowy moduł, który zapewnia niskie fluktuacje przy wyższych częstotliwościach, jednocześnie redukując miejsce zajmowane na płytce, koszty i czas wprowadzenia produktu na rynek.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.