Użycie układów SoC bezpośrednio programowalnych macierzy bramek (FPGA) w celu budowy bezpiecznych i połączonych systemów ścisłego czasu rzeczywistego

Przekazane przez: Północnoamerykańscy redaktorzy DigiKey

2023-02-16

Ważnymi narzędziami dla projektantów są bezpośrednio programowalne macierze bramek (FPGA), podsystemy mikrokontrolerów MCU RISC-V z obsługą systemu Linux, zaawansowane architektury pamięci oraz wysokowydajne interfejsy komunikacyjne. Dotyczy to w szczególności projektantów bezpiecznych systemów połączonych z siecią, systemów krytycznych dla bezpieczeństwa i szerokiej gamy systemów deterministycznych ścisłego czasu rzeczywistego, takich jak systemy sztucznej inteligencji (AI) i uczenia maszynowego (ML).

Jednak integracja tak różnorodnych elementów w bezpieczny, połączony oraz deterministyczny system może być trudnym i czasochłonnym działaniem, podobnie jak tworzenie szybkich połączeń dla różnych elementów tego systemu. Projektanci muszą pamiętać o jednostce zarządzania pamięcią, jednostce ochrony pamięci, funkcji bezpiecznego uruchamiania i nadajniko-odbiornikach gigabitowych zapewniających szybką łączność. Projekt będzie wymagał aktywnego i statycznego zarządzania zasilaniem oraz sterowania początkowymi prądami rozruchowymi. Niektóre projekty wymagają pracy w rozszerzonym, komercyjnym zakresie temperatur złącza (TJ) od 0°C do +100°C, podczas gdy systemy w środowiskach przemysłowych muszą pracować z temperaturą złącza TJ od -40°C do +100°C.

Aby sprostać tym i innym wyzwaniom, projektanci mogą skorzystać z układów SoC bezpośrednio programowalnych macierzy bramek (FPGA), które charakteryzują się niskim poborem mocy, sprawnością cieplną oraz zabezpieczeniami klasy wojskowej w celu stworzenia inteligentnych, połączonych i deterministycznych systemów.

W niniejszym artykule omówiono architekturę wspomnianego układu SoC bezpośrednio programowalnej macierzy bramek (FPGA) oraz sposób, w jaki wspiera on efektywne projektowanie połączonych i deterministycznych systemów. W dalszej części w skrócie przedstawiono test porównawczy EEMBC CoreMark-Pro mocy obliczeniowej w relacji do poboru mocy, a także wzorcowe parametry działania reprezentatywnego układu SoC bezpośrednio programowalnej macierzy bramek (FPGA). Artykuł omawia sposób implementacji zabezpieczeń w omawianych układach SoC bezpośrednio programowalnych macierzy bramek (FPGA) oraz szczegółowo omawia przykładowe układy SoC bezpośrednio programowalnych macierzy bramek (FPGA) firmy Microchip Technology wraz z platformą rozwojową przyspieszającą proces projektowania. Artykuł zamyka krótka lista płytek rozszerzeń firmy MikroElektronika, które można wykorzystać do wdrożenia szeregu interfejsów komunikacyjnych, a także funkcji lokalizacji z wykorzystaniem globalnego systemu nawigacji satelitarnej (GNSS).

Układ SoC zbudowany na sieci szkieletowej bezpośrednio programowalnej macierzy bramek (FPGA)

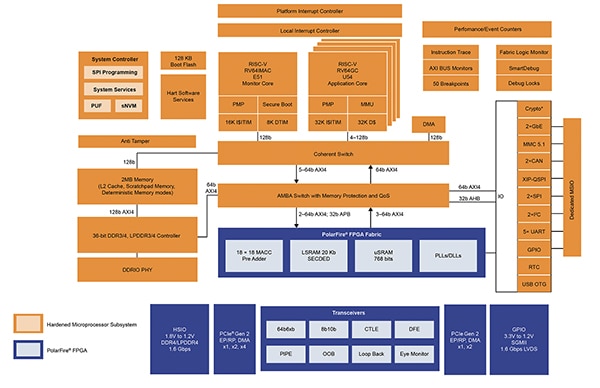

Mikroukładem dla omawianego układu SoC jest sieć szkieletowa bezpośrednio programowalnej macierzy bramek (FPGA), która zawiera elementy układowe, od bezpośrednio programowalnej macierzy bramek (FPGA) po podsystem mikrokontrolera MCU RISC-V zbudowany ze wzmocnionej logiki bezpośrednio programowalnej macierzy bramek (FPGA). Podsystem mikrokontrolera MCU obejmuje czterordzeniowy klaster mikrokontrolera MCU RISC-V, rdzeń monitora RISC-V, kontroler systemowy oraz deterministyczny podsystem pamięci poziomu 2 (L2). Bezpośrednio programowalna macierz bramek (FPGA) w omawianych układach SoC zawiera do 460K elementów logicznych, nadajniko-odbiorniki o prędkości transferu do 12,7Gbps oraz inne bloki wejścia-wyjścia (I/O), w tym bloki wejścia-wyjścia ogólnego przeznaczenia (GPIO) oraz interfejs połączeniowy komponentów peryferyjnych (PCIe) 2. Ogólna architektura została zaprojektowana z myślą o niezawodności. Zawiera ona korekcję błędu pojedynczego i wykrywanie błędu podwójnego (SECDED) we wszystkich pamięciach, różnicową analizę mocy (DPA), ochronę pamięci fizycznej oraz pamięć rozruchową flash 128kbit (ilustracja 1).

Ilustracja 1: wszystkie elementy składające się na układ SoC bezpośrednio programowalnej macierzy bramek, w tym podsystemy RISC-V, są zaimplementowane na sieci szkieletowej bezpośrednio programowalnej macierzy bramek (FPGA). (Źródło ilustracji: Microchip Technology)

Ilustracja 1: wszystkie elementy składające się na układ SoC bezpośrednio programowalnej macierzy bramek, w tym podsystemy RISC-V, są zaimplementowane na sieci szkieletowej bezpośrednio programowalnej macierzy bramek (FPGA). (Źródło ilustracji: Microchip Technology)

Firma Microchip oferuje własny ekosystem Mi-V (wymowa z angielskiego: „my five”) narzędzi i zasobów projektowych firm zewnętrznych wspierających wdrażanie układów RISC-V. Został on zaprojektowany tak, aby przyspieszyć wdrożenie architektury zestawu instrukcji RISC-V (ISA) dla wzmocnionych rdzeni RISC-V oraz rdzeni miękkich RISC-V. Ekosystem Mi-V daje dostęp do następujących zasobów:

- Licencje własności intelektualnej (IP)

- Sprzęt

- Systemy operacyjne i oprogramowanie pośredniczące

- Debuggery, kompilatory i usługi projektowe

Wzmocnione mikrokontrolery MCU RISC-V w układach SoC bezpośrednio programowalnych macierzy bramek (FPGA) zawierają kilka funkcji debugowania, jak np. pasywny konfigurowalny zaawansowany interfejs rozszerzalny (AXI) oraz zapis instrukcji. Dzięki zaawansowanemu interfejsowi rozszerzalnemu (AXI) projektanci mogą monitorować dane, które są zapisywane lub odczytywane z różnych pamięci oraz wiedzą, kiedy są one zapisywane lub odczytywane.

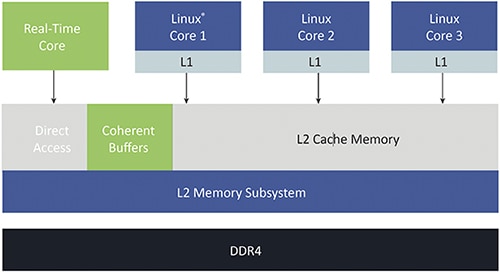

Architektura podsystemu mikrokontrolera MCU RISC-V charakteryzuje się pięciostopniową, skalarną budową i wykonywaniem operacji potoku w kolejności. Nie jest wrażliwa na programy wykorzystujące luki typu Spectre lub Meltdown, które mogą mieć wpływ na architektury z niesekwencyjnym wykonywaniem instrukcji. Wszystkie pięć mikrokontrolerów MCU jest spójnych z podsystemem pamięci i obsługuje kombinację deterministycznych systemów czasu rzeczywistego pracujących w trybie asymetryczne przetwarzanie wieloprocesorowe (AMP) oraz systemu Linux. Niektóre z możliwości podsystemu RISC-V to (ilustracja 2):

- Uruchamianie systemu Linux i operacji ścisłego czasu rzeczywistego

- Konfiguracja pamięci L1 i L2 jako pamięci deterministycznej

- Podsystem pamięci DDR4

- Włączanie i wyłączanie predyktorów odgałęzień

- Wykonywanie operacji potoku w kolejności

Ilustracja 2: podsystem RISC-V zawiera kilka elementów procesorowych i pamięciowych. (Źródło ilustracji: Microchip Technology)

Ilustracja 2: podsystem RISC-V zawiera kilka elementów procesorowych i pamięciowych. (Źródło ilustracji: Microchip Technology)

Większa moc obliczeniowa przy mniejszym zużyciu energii

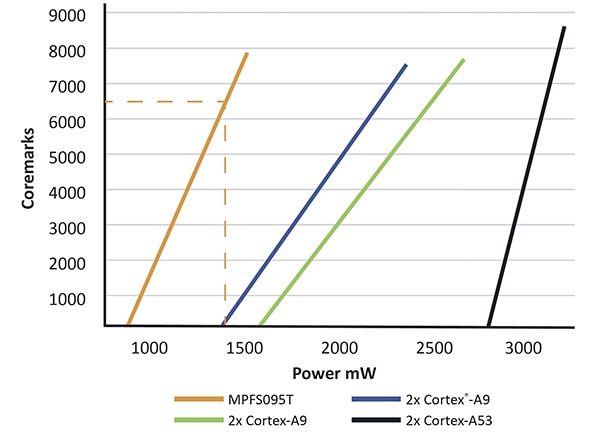

Poza korzyściami związanymi z działaniem systemu, takim jak obsługa przetwarzania ścisłego czasu rzeczywistego, omawiane układy SoC bezpośrednio programowalnych macierzy bramek (FPGA) charakteryzują się wysoką sprawnością energetyczną. Test porównawczy EEMBC CoreMark-PRO jest standardem branżowym porównującym sprawność i parametry działania mikrokontrolerów MCU w systemach wbudowanych. Został zaprojektowany specjalnie do testów porównawczych działania sprzętu i zastąpił test porównawczy Dhrystone.

Testy obciążeniowe CoreMark-PRO obejmują różnorodne charakterystyki parametrów działania, równoległość na poziomie instrukcji i wykorzystanie pamięci w oparciu o cztery obciążenia zmiennoprzecinkowe i pięć typowych obciążeń całkowitoliczbowych. Obciążenia zmiennoprzecinkowe obejmują liniową procedurę algebraiczną pochodzącą z biblioteki LINPACK, szybką transformację Fouriera, algorytm sieci neuronowej do ewaluacji wzorca oraz ulepszoną wersję testu pętli Livermore. Podstawę obciążeń całkowitoliczbowych stanowią kompresja JPEG, analizator XML, kompresja ZIP i 256-bitowy bezpieczny algorytm skrótu (SHA-256).

Modele MPFSO95T omawianych układów SoC bezpośrednio programowalnej macierzy bramek (FPGA), takich jak MPFS095TL-FCSG536E, są w stanie osiągnąć 6500 punktów CoreMark przy mocy 1,3W (ilustracja 3).

Ilustracja 3: układ SoC bezpośrednio programowalnej macierzy bramek (FPGA) MPFS095T (pomarańczowa linia) uzyskuje 6500 punktów Coremark przy mocy 1,3W. (Źródło ilustracji: Microchip Technology)

Ilustracja 3: układ SoC bezpośrednio programowalnej macierzy bramek (FPGA) MPFS095T (pomarańczowa linia) uzyskuje 6500 punktów Coremark przy mocy 1,3W. (Źródło ilustracji: Microchip Technology)

Kwestie dotyczące zabezpieczeń

Zastosowania kluczowe dla bezpieczeństwa i ścisłego czasu rzeczywistego omawianych układów SoC bezpośrednio programowalnych macierzy bramek (FPGA) oprócz wysokiej sprawności energetycznej i zaawansowanych możliwości przetwarzania wymagają silnych zabezpieczeń. Podstawowe funkcje zabezpieczeń omawianych układów SoC bezpośrednio programowalnych macierzy bramek (FPGA) to m.in. programowanie strumienia bitowego odporne na różnicową analizę mocy (DPA), generator liczb prawdziwie losowych (TRNG) i funkcja uniemożliwiająca fizycznie klonowanie (PUF). Obejmują one również standardowe i zdefiniowane przez użytkownika bezpieczne uruchamianie, ochronę pamięci fizycznej, która zapewnia ograniczenia dostępu do pamięci w zależności od stanu uprawnień komputera, w tym trybu maszyny, nadzorcy lub użytkownika, oraz odporność na ataki typu Meltdown i Spectre.

Zabezpieczenia zaczynają się od bezpiecznego zarządzania łańcuchem dostaw, w tym stosowania modułów zabezpieczeń sprzętowych (HSM) podczas testowania płytek i pakowania. Zastosowanie 768-bajtowego, podpisanego cyfrowo certyfikatu bezpośrednio programowalnej macierzy bramek (FPGA) X.509 osadzonego w każdym układzie SoC FPGA zwiększa niezawodność łańcucha dostaw.

W układach SoC bezpośrednio programowalnych macierzy bramek (FPGA) znajduje się wiele wbudowanych urządzeń do wykrywania nieautoryzowanych ingerencji, które zapewniają bezpieczne i niezawodne działanie. W przypadku wykrycia próby nieautoryzowanej ingerencji system może odpowiednio zareagować. Niektóre z dostępnych urządzeń do wykrywania nieautoryzowanej ingerencji:

- Monitory napięcia

- Czujniki temperatury

- Detektory zakłóceń zegara i częstotliwości zegara

- Aktywny detektor JTAG

- Aktywny detektor sieci kratowej

Bezpieczeństwo jest dodatkowo zapewnione dzięki środkom zapobiegającym atakom z wykorzystaniem korelacyjnej analizy mocy (CPA), wyposażonym w 256-bitowy symetryczny szyfr blokowy w zaawansowanym standardzie szyfrowania AES-256, zintegrowanym funkcjom skrótu kryptograficznego zapewniającym integralność danych, zintegrowanej funkcji uniemożliwiającej fizycznie klonowanie do przechowywania kluczy oraz możliwości wyzerowania sieci szkieletowej bezpośrednio programowalnej macierzy bramek (FPGA) i wszystkich pamięci w układzie.

Przykłady układów SoC bezpośrednio programowalnej macierzy bramek (FPGA)

Firma Microchip Technology łączy te możliwości i technologie w swoich układach SoC bezpośrednio programowalnych macierzy bramek (FPGA) PolarFire o różnych klasach prędkości, z różnymi parametrami temperaturowymi i różnymi rozmiarami obudów, które pozwalają zaspokoić potrzeby projektantów w szerokiej gamie rozwiązań z liczbą elementów logicznych od 25K do 460K. Dostępne są cztery klasy temperaturowe (wszystkie dla TJ), rozszerzony zakres komercyjny od 0°C do +100°C, zakres przemysłowy od -40°C do +100°C, zakres motoryzacyjny od -40°C do +125°C oraz zakres wojskowy od -55°C do +125°C.

Projektanci mogą dokonywać wyboru spośród urządzeń o standardowej klasie prędkości lub urządzeń o klasie prędkości -1, które są o 15% szybsze. Układy SoC bezpośrednio programowalnych macierzy bramek (FPGA) mogą być zasilane napięciem 1,0V w celu uzyskania najniższej mocy, lub napięciem 1,05V w celu uzyskania wyższych parametrów działania. Są one dostępne w obudowach o różnych rozmiarach, w tym 11 x 11mm, 16 x 16mm i 19 x 19mm.

W przypadku zastosowań wymagających rozszerzonego zakresu temperatur komercyjnych, pracy ze standardową prędkością oraz 254K elementów logicznych w obudowie 19 x 19mm, projektanci mogą sięgnąć po urządzenie MPFS250T-FCVG484EES. W przypadku prostszych rozwiązań wymagających 23K elementów logicznych, projektanci mogą skorzystać z urządzenia MPFS025T-FCVG484E, także z rozszerzonym zakresem temperatur roboczych i standardową prędkością, w obudowie 19 x 19mm. Urządzenie MPFS250T-1FCSG536T2 posiadające 254K elementów logicznych jest przeznaczone do wysokowydajnych systemów motoryzacyjnych i ma zakres temperatur roboczych od -40 do 125°C oraz klasę prędkości -1, co zapewnia o 15% szybszy zegar, w kompaktowej obudowie 16 x 16mm z 536 wyprowadzeniami sferycznymi na rastrze 0,5mm (ilustracja 4).

Ilustracja 4: urządzenie MPFS250T-1FCSG536T2 firmy Microchip do temperatur motoryzacyjnych jest dostępne w obudowie 16 x 16mm z 536 wyprowadzeniami sferycznymi i rastrem 0,5mm. (Źródło ilustracji: Microchip Technology)

Ilustracja 4: urządzenie MPFS250T-1FCSG536T2 firmy Microchip do temperatur motoryzacyjnych jest dostępne w obudowie 16 x 16mm z 536 wyprowadzeniami sferycznymi i rastrem 0,5mm. (Źródło ilustracji: Microchip Technology)

Platforma rozwojowa układu SoC bezpośrednio programowalnej macierzy bramek (FPGA)

Aby przyspieszyć projektowanie systemów z wykorzystaniem układu SoC bezpośrednio programowalnej macierzy bramek (FPGA) PolarFire, firma Microchip oferuje zestaw MPFS-ICICLE-KIT-ES PolarFire SoC Icicle, który umożliwia analizę działania pięciordzeniowego podsystemu mikroprocesorowego RISC-V z obsługą systemu Linux i możliwością wykonywania operacji w czasie rzeczywistym przy niskiej mocy. Zestaw zawiera bezpłatną licencję Libero Silver, która jest potrzebna do ewaluacji projektów. Obsługuje ona funkcje programowania i debugowania w jednym języku.

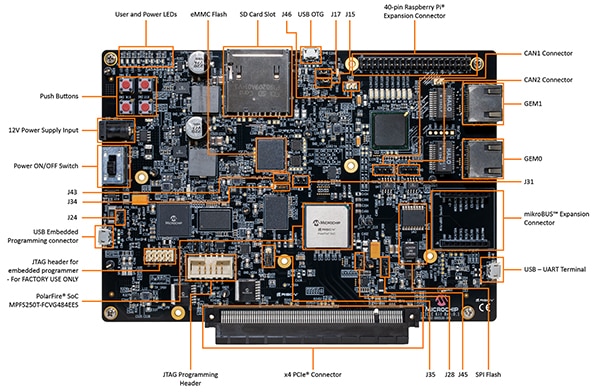

Pracę z układami SoC bezpośrednio programowalnych macierzy bramek (FPGA) wspomaga akceleratorowy zestaw rozwojowy oprogramowania (SDK) VectorBlox, który pozwala na opracowywanie kompaktowych rozwiązań niskiej mocy ze sztuczną inteligencją i uczeniem maszynowym (AI/ML). Nacisk kładziony jest na uproszczenie procesu projektowania do tego stopnia, że projektanci nie muszą mieć wcześniejszego doświadczenia w projektowaniu bezpośrednio programowalnych macierzy bramek (FPGA). Akceleracyjny zestaw rozwojowy oprogramowania (SDK) VectorBlox umożliwia deweloperom programowanie energooszczędnych sieci neuronowych przy użyciu języka C/C++. Zestaw Icicle posiada wiele funkcji tworzących kompleksowe środowisko programistyczne, w tym system czujników z zasilaniem wieloszynowym do monitorowania różnych stref zasilania, główny port PCIe, różne pamięci wbudowane - w tym LPDDR4, QSPI i eMMC Flash - do obsługi systemów Linux i Raspberry Pi oraz porty rozszerzeń mikroBUS na potrzeby wielu opcji łączności przewodowej i bezprzewodowej oraz rozszerzenia funkcjonalne, takie jak funkcja lokalizacji wykorzystująca globalny system nawigacji satelitarnej (GNSS) (ilustracja 5).

Ilustracja 5: w przedstawianym kompleksowym środowisku rozwojowym do układów SoC bezpośrednio programowalnych macierzy bramek (FPGA) znajdują się złącza do płytek rozszerzeń Raspberry Pi (u góry po prawej) i mikroBUS (u dołu po prawej stronie). (Źródło ilustracji: Microchip Technology)

Ilustracja 5: w przedstawianym kompleksowym środowisku rozwojowym do układów SoC bezpośrednio programowalnych macierzy bramek (FPGA) znajdują się złącza do płytek rozszerzeń Raspberry Pi (u góry po prawej) i mikroBUS (u dołu po prawej stronie). (Źródło ilustracji: Microchip Technology)

Płytki rozszerzeń

Kilka przykładów płytek rozszerzeń mikroBUS:

MIKROE-986 -zapewnienie dodatkowej łączności przez magistralę CAN z wykorzystaniem szeregowego interfejsu urządzeń peryferyjnych (SPI).

MIKROE-1582 - interfejs pomiędzy mikrokontrolerem MCU i magistralą RS-232.

MIKROE-989 - łączenie z magistralą komunikacyjną RS422/485.

MIKROE-3144 - obsługa technologii LTE kat. M1 i NB1 umożliwiająca niezawodną i prostą łączność z urządzeniami Internetu rzeczy (IoT) 3GPP.

MIKROE-2670 - dodanie funkcji lokalizacji z wykorzystaniem globalnego systemu nawigacji satelitarnej (GNSS) z równoczesnym odbiorem konstelacji systemów GPS i Galileo oraz BeiDou lub GLONASS, zapewniające wysoką dokładność pozycji w przypadku słabego sygnału lub zakłóceń w miejskich kanionach.

Podsumowanie

Podczas opracowywania połączonych, krytycznych dla bezpieczeństwa deterministycznych systemów ścisłego czasu rzeczywistego, projektanci mogą sięgnąć po układy SoC bezpośrednio programowalnych macierzy bramek (FPGA). Układy SoC bezpośrednio programowalnych macierzy bramek (FPGA) zapewniają szeroką gamę elementów systemowych, w tym sieć szkieletową FPGA, podsystem mikrokontrolera MCU RISC-V z pamięciami o wysokich parametrach działania, szybkie interfejsy komunikacyjne i liczne funkcje zabezpieczeń. W rozpoczęciu pracy projektantom mogą pomóc dostępne płytki i środowiska rozwojowe zawierające wszystkie niezbędne elementy, w tym płytki rozszerzeń, których można używać do wdrażania szerokiego zakresu funkcji komunikacyjnych i lokalizacyjnych.

Rekomendowane artykuły

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.