Szybsze projektowanie wizyjnych systemów rozpoznawania dzięki mikroprocesorom serii RZ/V2 firmy Renesas

Przekazane przez: Północnoamerykańscy redaktorzy DigiKey

2022-09-29

Ponieważ rozpoznawanie wizyjne w środowisku brzegowym staje się coraz bardziej krytyczną cechą wielu produktów, uczenie maszynowe (ML) i sztuczna inteligencja (AI) trafiają do szerokiej gamy zastosowań. Deweloperzy mierzą się z problemami, które polegają na tym, że widzenie z uczeniem maszynowym i sztuczną inteligencją (ML/AI) może wymagać większej mocy obliczeniowej do uruchomienia algorytmów rozpoznawania, niż dostępna w przypadku zastosowań o ograniczonej mocy. Koszty również rosną w przypadku konieczności zastosowania drogich rozwiązań odprowadzania ciepła.

Celem zastosowania technologii uczenia maszynowego i sztucznej inteligencji (ML/AI) w środowisku brzegowym jest znalezienie optymalnej architektury zapewniającej zrównoważenie parametrów działania i mocy, a jednocześnie stanowiącej solidny ekosystem oprogramowania do rozwijania aplikacji.

Niniejszy artykuł uwzględnia te warunki i przedstawia rozwiązanie w postaci mikroprocesora (MPU) RZ/V2 firmy Renesas Electronics z wbudowanym akceleratorem sprzętowym sztucznej inteligencji. W artykule omówiono, w jaki sposób wykorzystanie mikroprocesora (MPU) zamiast mikrokontrolera (MCU) czy wysokiej klasy procesora graficznego (GPU) pozwala rozwiązać szereg problemów, z którymi borykają się projektanci. Przygotowano także opis sposobu, w jaki mogą oni rozpocząć projektowanie wizyjnych systemów rozpoznawania przy użyciu urządzeń z serii RZ/V2, oraz kilka porad i wskazówek ułatwiających proces.

Wprowadzenie do mikroprocesorów serii RZ/V2

Trójrdzeniowe mikroprocesory z serii RZ/V2 dają deweloperom zupełnie nowe możliwości. Mikroprocesory z serii RZ/V2L zawierają dwa procesory Arm Cortex-A55 pracujące z częstotliwością 1,2GHz oraz rdzeń mikrokontrolera czasu rzeczywistego (ARM® Cortex®-M33) pracujący z częstotliwością 200MHz. Ponadto komponenty z tej serii zawierają procesor graficzny (GPU) oparty na procesorze multimedialnym Arm Mali-G31 z jedną lub wieloma instrukcjami NEON (SIMD). Kombinacja tych trzech rdzeni przetwarzania i procesora multimedialnego stanowi doskonałe rozwiązanie dla deweloperów pracujących nad wizyjnymi systemami rozpoznawania.

Obecnie seria RZ/V2 obejmuje dwie klasy mikroprocesorów (MPU): serię RZ/V2L i serię RZ/V2M. Urządzenia RZ/V2L posiadają prosty procesor sygnału obrazu (ISP), silnik grafiki 3D i bardzo wszechstronny zestaw urządzeń peryferyjnych. Seria RZ/V2M z kolei zawiera wysokowydajny procesor sygnału obrazu, który obsługuje rozdzielczość 4K przy częstotliwości 30fps. W artykule skupiono się na grupie RZ/V2L, składającej się z mikroprocesorów R9A07G054L23GBG i R9A07G054L24GBG. Główną różnicą między wspomnianymi dwoma urządzeniami jest to, że model R9A07G054L23GBG jest dostarczany w obudowie 15mm2, 456-LFBGA, a model R9A07G054L24GBG jest dostarczany w obudowie 21mm2, 551-LFBGA.

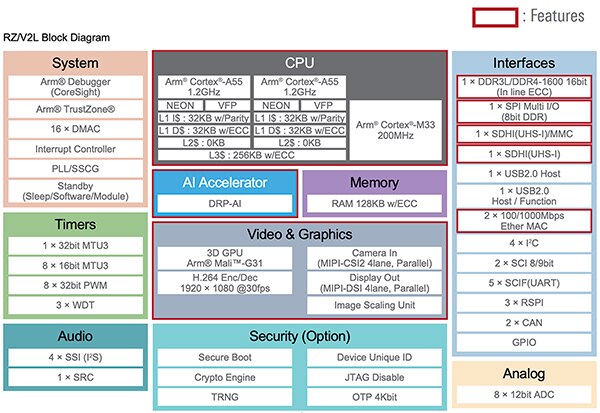

Schemat blokowy dla serii RZ/V2L przedstawia ilustracja 1. Oprócz trzech rdzeni przetwarzania omawiane mikroprocesory posiadają także interfejsy dla standardowych urządzeń peryferyjnych, takich jak pamięć DDR3/DDR4, szeregowy interfejs urządzeń peryferyjnych (SPI), port USB, Ethernet, I²C, CAN, SCI, wejście-wyjście ogólnego przeznaczenia (GPIO) i przetwornik analogowo-cyfrowy (ADC). Ponadto wyposażone są w takie zabezpieczenia, jak bezpieczne uruchamianie, aparat kryptograficzny i generator liczb losowych (TRNG). Tym, co wyróżnia serię mikroprocesorów, jest jednak akcelerator sztucznej inteligencji z dynamicznie rekonfigurowalnym procesorem (DRP).

Ilustracja 1: seria mikroprocesorów RZ/V2L obsługuje różne interfejsy urządzeń peryferyjnych, zabezpieczenia i opcje przetwarzania obrazu. Kluczową cechą wizyjnych aplikacji rozpoznawania jest akcelerator sztucznej inteligencji z dynamicznie rekonfigurowalnym procesorem (DRP-AI). (Źródło ilustracji: Renesas Electronics Corporation)

Ilustracja 1: seria mikroprocesorów RZ/V2L obsługuje różne interfejsy urządzeń peryferyjnych, zabezpieczenia i opcje przetwarzania obrazu. Kluczową cechą wizyjnych aplikacji rozpoznawania jest akcelerator sztucznej inteligencji z dynamicznie rekonfigurowalnym procesorem (DRP-AI). (Źródło ilustracji: Renesas Electronics Corporation)

Akcelerator DRP-AI - tajny składnik

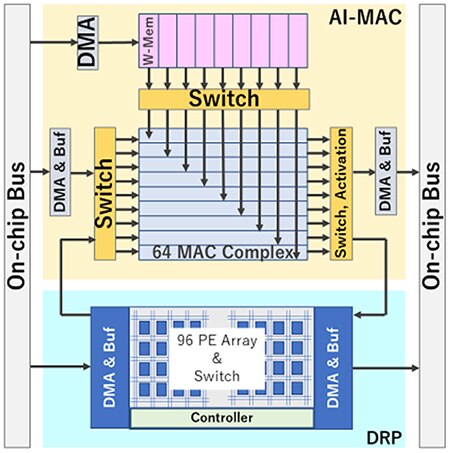

Akcelerator sztucznej inteligencji z dynamicznie rekonfigurowalnym procesorem (DRP-AI) jest tym tajnym składnikiem, który umożliwia mikroprocesorowi serii RZ/V2L szybkie wykonywanie wizyjnych aplikacji rozpoznawania, przy mniejszym zużyciu energii i niższym profilu termicznym. Akcelerator DRP-AI składa się z dwóch elementów: dynamicznie rekonfigurowalnego procesora (DRP) i jednostki mnożąco-akumulującej ze sztuczną inteligencją (AI-MAC), które potrafią efektywnie realizować operacje w sieciach konwolucyjnych i wszystkich połączonych warstwach dzięki optymalizacji przepływu danych z wykorzystaniem wewnętrznych przełączników (ilustracja 2).

Sprzęt akceleratora DRP-AI ma za zadanie realizację wnioskowania z wykorzystaniem sztucznej inteligencji. Akcelerator DRP-AI wykorzystuje unikatową, dynamiczną technologię rekonfiguracji opracowaną przez firmę Renesas, która zapewnia elastyczność, szybkie przetwarzanie i sprawność energetyczną. Ponadto bezpłatne narzędzie programowe translatora DRP-AI pozwala użytkownikom na wdrożenie zoptymalizowanych modeli sztucznej inteligencji (AI), które szybko maksymalizują parametry działania. W pamięci zewnętrznej można umieścić wiele plików wyjściowych translatora DRP-AI. Aplikacja może wtedy dynamicznie przełączać się pomiędzy wieloma modelami sztucznej inteligencji podczas pracy.

Dzięki dynamicznej konfiguracji sprzętowej, dynamicznie rekonfigurowalny procesor (DRP) potrafi szybko wykonywać złożone działania, takie jak przetwarzanie wstępne obrazów i łączenie warstw w modelu sztucznej inteligencji.

Ilustracja 2: akcelerator DRP-AI składa się z dynamicznie rekonfigurowalnego procesora (DRP) i jednostki mnożąco-akumulującej ze sztuczną inteligencją (AI-MAC), które łącznie potrafią sprawnie obsługiwać operacje w sieciach konwolucyjnych i łączyć warstwy poprzez optymalizację przepływu danych za pomocą wewnętrznych przełączników. (Źródło ilustracji: Renesas Electronics Corporation)

Ilustracja 2: akcelerator DRP-AI składa się z dynamicznie rekonfigurowalnego procesora (DRP) i jednostki mnożąco-akumulującej ze sztuczną inteligencją (AI-MAC), które łącznie potrafią sprawnie obsługiwać operacje w sieciach konwolucyjnych i łączyć warstwy poprzez optymalizację przepływu danych za pomocą wewnętrznych przełączników. (Źródło ilustracji: Renesas Electronics Corporation)

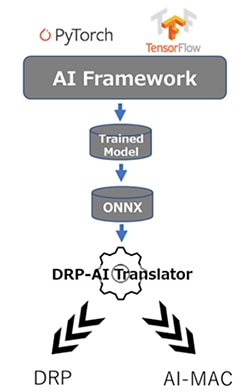

Narzędzie DRP-AI Translator

Narzędzie DRP-AI Translator generuje zoptymalizowane przez akcelerator DRP-AI pliki wykonywalne na podstawie przeszkolonych modeli ONNX, nie zależnie od środowiska sztucznej inteligencji (AI). Deweloperzy mogą na przykład użyć środowiska modelowania sztucznej inteligencji PyTorch, TensorFlow lub innego, pod warunkiem, że wynikowym modelem będzie model ONNX. Po przeszkoleniu model jest przesyłany do narzędzia DRP-AI Translator, które generuje pliki wykonywalne DRP i AI-MAC (ilustracja 3).

Ilustracja 3: modele sztucznej inteligencji są szkolone przy użyciu dowolnego środowiska zgodnego z ONNX. Model ONNX jest następnie przesyłany do narzędzia DRP-AI Translator, który generuje pliki wykonywalne DRP i AI-MAC. (Źródło ilustracji: Renesas Electronics Corporation)

Ilustracja 3: modele sztucznej inteligencji są szkolone przy użyciu dowolnego środowiska zgodnego z ONNX. Model ONNX jest następnie przesyłany do narzędzia DRP-AI Translator, który generuje pliki wykonywalne DRP i AI-MAC. (Źródło ilustracji: Renesas Electronics Corporation)

Narzędzie DRP-AI Translator ma trzy podstawowe cele:

- Planowanie poszczególnych operacji w celu przetworzenia modelu sztucznej inteligencji.

- Ukrywanie elementów pośrednich, takich jak czas dostępu do pamięci, który występuje podczas realizacji każdej operacji w harmonogramie.

- Optymalizacja struktury grafów sieci.

Translator automatycznie przypisuje poszczególne procesy modelu sztucznej inteligencji do dynamicznie rekonfigurowalnego procesora (DRP) i jednostki mnożąco-akumulującej ze sztuczną inteligencją (AI-MAC), umożliwiając łatwe korzystanie z akceleratora DRP-AI użytkownikom nie będącym ekspertami w dziedzinie sprzętu. Zamiast tego deweloper może realizować wywołania za pośrednictwem dostarczonego sterownika w celu uruchomienia wydajnego modelu sztucznej inteligencji. Ponadto translator DRP-AI można aktualizować na bieżąco w celu obsługi nowo opracowanych modeli sztucznej inteligencji bez konieczności zmian w sprzęcie.

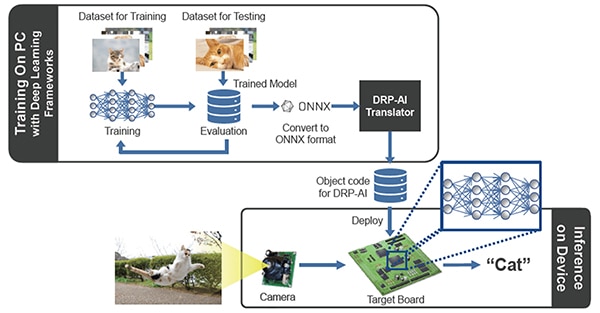

Procesy i przykłady wykorzystania systemu

Ogólny przepływ procesu wykorzystania mikroprocesorów RZ/V2L do szkolenia i wdrażania wizyjnych aplikacji rozpoznawania przedstawiono na ilustracji 4. Jak zwykle inżynierowie mogą zakupić zestaw danych i wykorzystywać go do szkolenia swojego wizyjnego modelu rozpoznawania. Nie ma znaczenia, czy będzie on służyć do identyfikacji kotów, produktów w koszyku czy części na linii montażowej, proces szkolenia będzie przebiegał przy użyciu znanych środowisk sztucznej inteligencji. Po przeszkoleniu model jest konwertowany na format ONNX i przekazywany do narzędzia DRP-AI, które z kolei generuje kod obiektowy, który może być wykonywany na akceleratorze DRP-AI. Następnie pobierane są próbki danych z kamer, akcelerometrów lub innych czujników, a następnie są one podawane do plików wykonywalnych, co w rezultacie stanowi wynik wnioskowania.

Ilustracja 4: proces szkolenia i uruchamiania wizyjnego algorytmu rozpoznawania w przypadku mikroprocesorów RZ/V2L. (Źródło ilustracji: Renesas Electronics Corporation)

Ilustracja 4: proces szkolenia i uruchamiania wizyjnego algorytmu rozpoznawania w przypadku mikroprocesorów RZ/V2L. (Źródło ilustracji: Renesas Electronics Corporation)

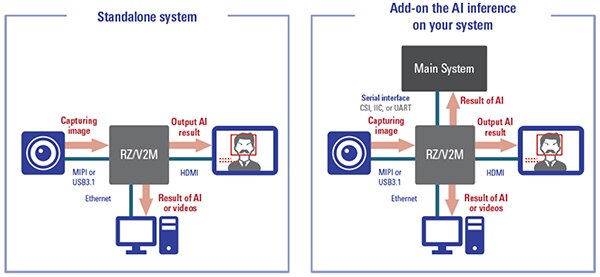

Istnieje kilka sposobów, w jaki inżynierowie mogą wykorzystać mikroprocesory RZ/V2L w swoich projektach (ilustracja 5). Po pierwsze, mikroprocesor RZ/V2L może być używany jako jedyny procesor w projekcie autonomicznym. Dzięki zastosowaniu trzech rdzeni i sprzętu akceleracyjnego sztucznej inteligencji dodatkowa moc obliczeniowa może nie być potrzebna.

Z innym przypadkiem zastosowania mamy do czynienia, gdy mikroprocesor RZ/V2L jest używany jako procesor sztucznej inteligencji w bardziej rozbudowanym systemie. W takim przypadku w mikroprocesorze RZ/V2L uruchamiane są procesy wnioskowania z wykorzystaniem sztucznej inteligencji, a wyniki są zwracane do innego procesora lub układu, który następnie wykonuje działania w oparciu o ten wynik. Wybrany przypadek wykorzystania będzie zależeć od różnych czynników, takich jak koszt, ogólna architektura układu, parametry działania i wymagania dotyczące odpowiedzi w czasie rzeczywistym.

Ilustracja 5: dwa przypadki wykorzystania mikroprocesorów RZ/V2L polegają na autonomicznym ich użyciu w rozwiązaniu lub jako procesorów sztucznej inteligencji używanych w bardziej rozbudowanym systemie. (Źródło ilustracji: Renesas Electronics Corporation)

Ilustracja 5: dwa przypadki wykorzystania mikroprocesorów RZ/V2L polegają na autonomicznym ich użyciu w rozwiązaniu lub jako procesorów sztucznej inteligencji używanych w bardziej rozbudowanym systemie. (Źródło ilustracji: Renesas Electronics Corporation)

Przykładowe rzeczywiste wykorzystanie

Istnieje wiele przypadków zastosowania wizyjnej technologii rozpoznawania. Ciekawym przykładem jest supermarket. W dzisiejszych czasach przy kasach w sklepach spożywczych ekspedient lub klient zazwyczaj skanuje każdy przedmiot w koszyku. Interesującym przykładem zastosowania mikroprocesora jest wykrywanie produktów układanych na taśmie, do realizacji wizyjnej funkcji rozpoznawania i automatycznego pobierania opłat.

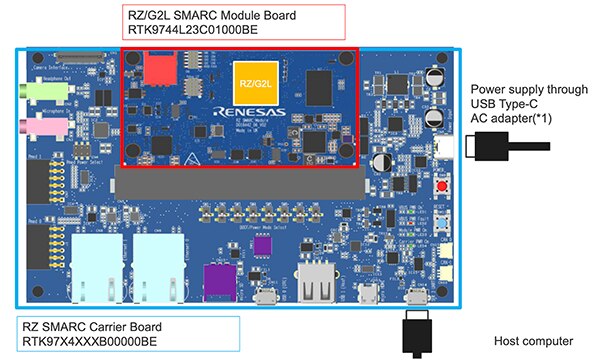

Prototyp można zbudować przy użyciu prostej kamery CMOS i płytki ewaluacyjnej RTK9754L23S01000BE firmy Renesas (ilustracja 6). Wbudowana płytka rozwojowa RZ/V2L posiada moduł SOM (System-on-Module) i płytkę nośną, które pozwalają deweloperom na szybkie rozpoczęcie pracy. Ponadto płytka rozwojowa obsługuje system Linux, a także różne narzędzia, takie jak DRP-AI Translator.

Ilustracja 6: wbudowana płytka rozwojowa RZ/V2L posiada moduł SOM (System-on-Module) i płytkę nośną, pozwalające deweloperom szybko zacząć pracę. (Źródło ilustracji: Renesas Electronics Corporation)

Ilustracja 6: wbudowana płytka rozwojowa RZ/V2L posiada moduł SOM (System-on-Module) i płytkę nośną, pozwalające deweloperom szybko zacząć pracę. (Źródło ilustracji: Renesas Electronics Corporation)

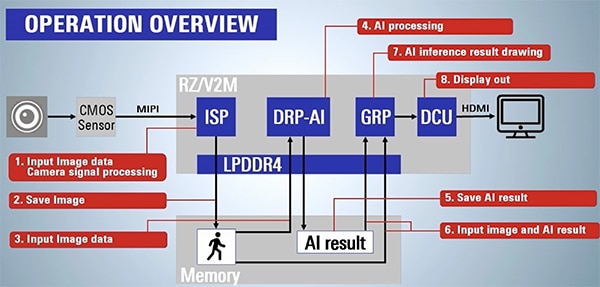

Roboczy przegląd informacji wymaganych do akwizycji danych obrazu i uzyskania wyniku działania sztucznej inteligencji można zobaczyć na ilustracji 7. W tym przykładzie wykorzystania czujnik z matrycą CMOS wykonuje zdjęcia taśmy przenośnikowej poprzez zintegrowany podsystem obrazowania (ISP). Następnie obraz jest zapisywany w pamięci i przekazywany do aparatu DRP-AI. Na koniec aparat DRP-AI przeprowadza wnioskowanie i dostarcza rezultat pracy sztucznej inteligencji. Na przykład rezultatem może być wykrycie banana, jabłka lub innego owocu.

Rezultat często charakteryzuje się poziomem ufności od 0 do 1. Na przykład pewność 0,90 oznacza, że sztuczna inteligencja ma pewność, że wykryła jabłko. Z kolei pewność 0.52 może oznaczać, że sztuczna inteligencja uważa, że jest to jabłko, ale nie ma co do tego pewności. Czasami rezultaty pracy sztucznej inteligencji dla wielu próbek są uśredniane, aby zwiększyć szanse na uzyskanie prawidłowych wyników.

Ilustracja 7: wbudowana płytka rozwojowa RZ/V2L służy do realizacji wnioskowania z wykorzystaniem sztucznej inteligencji, którego zadanie polega a rozpoznawaniu różnych owoców na taśmie. Ilustracja przedstawia czynności niezbędne do akwizycji obrazu i uzyskania rezultatu działania sztucznej inteligencji. (Źródło ilustracji: Renesas Electronics Corporation)

Ilustracja 7: wbudowana płytka rozwojowa RZ/V2L służy do realizacji wnioskowania z wykorzystaniem sztucznej inteligencji, którego zadanie polega a rozpoznawaniu różnych owoców na taśmie. Ilustracja przedstawia czynności niezbędne do akwizycji obrazu i uzyskania rezultatu działania sztucznej inteligencji. (Źródło ilustracji: Renesas Electronics Corporation)

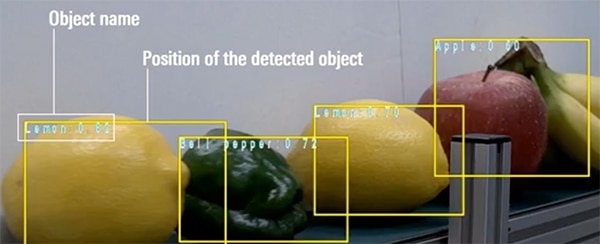

Na koniec w omawianym przykładzie wokół wykrytego obiektu rysowana jest ramka i wyświetlana jest nazwa rozpoznanego obiektu wraz z poziomem ufności (ilustracja 8).

Ilustracja 8: przykładowy rezultat działania mikroprocesora RZ/V2L w rozwiązaniu wykrywającym owoce i warzywa na taśmie przenośnika. (Źródło ilustracji: Renesas Electronics Corporation)

Ilustracja 8: przykładowy rezultat działania mikroprocesora RZ/V2L w rozwiązaniu wykrywającym owoce i warzywa na taśmie przenośnika. (Źródło ilustracji: Renesas Electronics Corporation)

Wskazówki i porady dotyczące rozpoczęcia pracy z mikroprocesorem RZ/V2L

Deweloperzy, którzy chcą rozpocząć pracę z uczeniem maszynowym z wykorzystaniem mikroprocesorów RZ/V2L firmy Renesas, przekonają się, jak dużą ilość zasobów pozwalających im rozpocząć pracę mają do dyspozycji. Oto kilka wskazówek i porad, o których deweloperzy powinni pamiętać oraz które uproszczą i przyspieszą prace rozwojowe:

- Zacznij od płytki rozwojowej i istniejących przykładów, aby wczuć się w temat wdrażania i uruchamiania rozwiązań.

- Jeśli konieczne jest wykonanie wielu procesów wnioskowania, zapisz modele plików do pamięci zewnętrznej i użyj funkcji DRP-AI do szybkiego przełączania między modelami.

- Zapoznaj się z dokumentacją i filmami wideo w witrynie poświęconej wbudowanym mikroprocesorom sztucznej inteligencji RZ/V firmy Renesas.

- Pobierz narzędzie DRP-AI Translator.

- Pobierz pakiet pomocniczy RZ/V2L DRP-AI.

Deweloperzy, którzy zastosują się do powyższych wskazówek i porad, oszczędzą sobie sporo czasu i irytacji przy rozpoczynaniu pracy.

Podsumowanie

Uczenie maszynowe (ML) i sztuczna inteligencja (AI) znajdują zastosowanie w wielu rozwiązaniach brzegowych, a ich zdolność do rozpoznawania obiektów w czasie rzeczywistym staje się coraz istotniejsza. Dla projektantów trudność polega na znalezieniu właściwej architektury, którą można wykorzystać do uruchomienia funkcji sztucznej inteligencji i uczenia maszynowego (AI/ML) w środowisku brzegowym. Procesory graficzne (GPU) zazwyczaj zużywają dużo mocy, z kolei moc obliczeniowa mikroprocesorów może nie być wystarczająca.

Seria mikroprocesorów RZ/V firmy Renesas z funkcją DRP-AI posiada kilka zalet, takich jak akceleracja sprzętowa sztucznej inteligencji oraz bogaty łańcuch narzędziowy, a także obsługa prototypowania.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.